Hardware Manual - phyCORE-i.MX 8M Mini/phyBOARD-Polis (1518.1a/1532.1) (L-862e.A2)

Table of Contents

Copyrighted products are not explicitly indicated in this manual. The absence of the trademark (™ or ®) and copyright (©) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

The information in this document has been carefully checked and is considered to be entirely reliable. However, PHYTEC Messtechnik GmbH assumes no responsibility for any inaccuracies. PHYTEC Messtechnik GmbH neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC Messtechnik GmbH reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages that might result.

Additionally, PHYTEC Messtechnik GmbH offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC Messtechnik GmbH further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

@ Copyright 2021 PHYTEC Messtechnik GmbH, D-55129 Mainz.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC Messtechnik GmbH.

| EUROPE | NORTH AMERICA | FRANCE | INDIA | CHINA |

Address: | PHYTEC Messtechnik GmbH | PHYTEC America LLC | PHYTEC France | PHYTEC Embedded Pvt. Ltd | PHYTEC Information Technology (Shenzhen) Co. Ltd. |

Ordering Information: | +49 6131 9221-32 | +1 800 278-9913 | +33 2 43 29 22 33 | +91-80-4086 7046/48 sales@phytec.in | +86-755-3395-5875 sales@phytec.cn |

Technical Support: | +49 6131 9221-31 | +1 206 780-9047 | +91-80-4086 7047 support@phytec.in | support@phytec.cn | |

Fax: | +49 6131 9221-33 | +1 206 780-9135 | +33 2 43 29 22 34 | +86-755-3395-5999 | |

Web Site: | http://phytec.in | http://www.phytec.cn |

Conventions, Abbreviations, and Acronyms

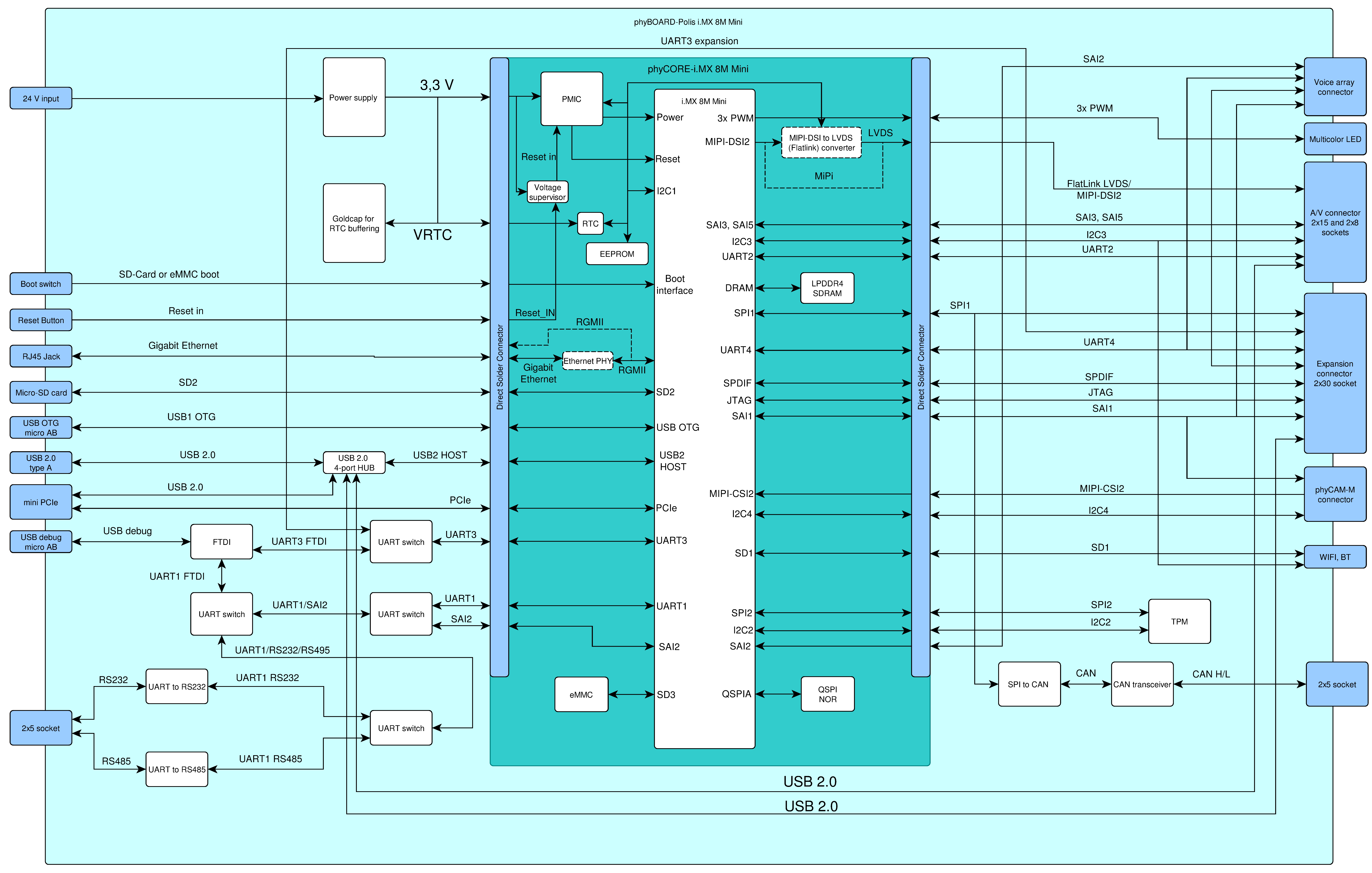

This hardware manual describes the PCL-069 System on Module, referred to as phyCORE®-i.MX 8M Mini, and the PB-02820-xxxxx.Ax, referred to as phyBOARD®-Polis. The manual specifies the phyCORE-i.MX 8M Mini and phyBOARD-Polis' design and function. Precise specifications for the NXP® Semiconductor i.MX 8M Mini microcontrollers can be found in thei.MX 8M Mini Microcontroller Data Sheet/Reference Manual.

Tip

Due to part maintenance for our products (which are subject to continuous changes), we refrain from providing detailed, part-specific information within this manual. Please read the section Product Change Management and Information Regarding Parts Populated on the SOM / SBC within the Preface for more information.

Tip

The BSP delivered with the phyCORE-i.MX 8M Mini includes drivers and/or software for controlling all components such as interfaces, memory, etc. Programming close to hardware at register level is not necessary in most cases. For this reason, this manual contains no detailed description of the controller's registers or information relevant to software development. Please refer to the NXP i.MX 8M Mini Reference Manual, if such information is needed to connect customer-designed applications.

Conventions

The conventions used in this manual are as follows:

- Signals that are preceded by an "n", "/", or “#”character (e.g.: nRD, /RD, or #RD), or that have a dash on top of the signal name (e.g.: RD) are designated as active low signals. That is, their active state is when they are driven low, or are driving low.

- A "0" indicates a logic zero or low-level signal, while a "1" represents a logic one or high-level signal.

- The hex-numbers given for addresses of I2C devices always represent the 7 MSB of the address byte. The correct value of the LSB which depends on the desired command (read (1), or write (0)) must be added to get the complete address byte. E.g. given address in this manual 0x41 => complete address byte = 0x83 to read from the device and 0x82 to write to the device

- Tables that describe jumper settings show the default position in bold,bluetext.

Types of Signals

Different types of signals are brought out at the phyCORE-Connector. The following table lists the abbreviations used to specify the type of signal.

| Signal Type | Description | Abbreviation |

|---|---|---|

| Power | Supply voltage input | PWR_I |

| Ref-Voltage | Reference voltage output | REF_O |

| Input | Digital input | I |

| Input-Pullup | Input with pull up | I-PU |

| Output | Digital output | O |

| IO | Bidirectional input/output | I/O |

| OC-Bidir | Open collector input/output with pull up | OC-BI |

| OC-Output | Open collector output without pull up, requires an external pull up | OC |

| OD-Bidir PU | Open drain input/output with pull up | OD-BI |

| OD-Output | Open drain output without pull up, requires an external pull up | OD |

| OD-Output-Pullup | Open drain output with pull up | OD-PU |

| 5V Input PD | 5 V tolerant input with pull down | 5V_PD |

| USB IO | Differential line pairs 90 Ohm USB level bidirectional input/output | USB_I/O |

| ETHERNET Input | Differential line pairs 100 Ohm Ethernet level input | ETH_I |

| ETHERNET Output | Differential line pairs 100 Ohm Ethernet level output | ETH_O |

| ETHERNET IO | Differential line pairs 100 Ohm Ethernet level bidirectional input/output | ETH_I/O |

| PCIe Input | Differential line pairs 85 Ohm PCIe level input | PCIe_I |

| PCIe Output | Differential line pairs 85 Ohm PCIe level output | PCIe_O |

| MIPI CSI-2 Input | Differential line pairs 100 Ohm MIPI CSI‑2 level input | CSI2_I |

| MIPI DSI-2 Output | Differential line pairs 100 Ohm MIPI DSI-2 level input | DSI2_O |

| CAN FD IO | Differential line pairs 120 Ohm | CAN_I/O |

| CAN FD IO | Differential line pairs 120 Ohm | CAN_I/O |

| Wireless | Wireless signal input/output | WL_I/O |

Abbreviations and Acronyms

Many acronyms and abbreviations are used throughout this manual. Use the table below to navigate any unfamiliar terms used in this document.

| Abbreviation | Definition |

|---|---|

| BGA | Ball Grid Array |

BSP | Board Support Package (software delivered with the Development Kit including an operating system (Windows or Linux) preinstalled on the module and development tools) |

CB | Carrier board; used in reference to the phyCORE development kit carrier board |

EMI | Electromagnetic Interference |

GPI | General-purpose input |

GPIO | General-purpose input and output |

GPO | General-purpose output |

IRAM | Internal RAM; the internal static RAM on the NXP® Semiconductor i.MX 8M microcontroller |

J | Solder jumper; these types of jumpers require solder equipment to remove and place |

JP | Solderless jumper; these types of jumpers can be removed and placed by hand with no special tools |

| OEM | Original Equipment Manufacturers |

PCB | Printed circuit board |

| PCM | Product Change Management |

| PCN | Product Change Notification |

PMIC | Power management IC |

RTC | Real-time clock |

| SBC | Single Board Computer |

SMT | Surface mount technology |

SOM | System on Module; used in reference to the PCL-066 /phyCORE®-i.MX 8M module |

Sx | User button Sx (e.g. S1, S2, etc.) used in reference to the available user buttons, or DIP-Switches on the carrier board |

Sx_y | Switch y of DIP-Switch Sx; used in reference to the DIP-Switch on the carrier board |

| VM | Virtual Machine |

Abbreviations and Acronyms Used in this Manual

Preface

As a member of PHYTEC's phyCORE® product family, the phyCORE‑i.MX 8M Mini is one of a series of PHYTEC System on Modules (SOMs) that can be populated with different controllers, various types of memory (RAM, NAND flash, eMMC), and many other features. This, in turn, offers increased kinds of functions and configurations. PHYTEC supports a variety of 8/16/32/64 bit controllers in two ways:

- As the basis for Rapid Development Kits which serve as a reference and evaluation platform.

- As insert-ready, fully functional phyCORE® OEM modules, which can be embedded directly into the user’s peripheral hardware design.

Implementation of an OEM-able SOM subassembly as the "core" of your embedded design allows for increased focus on hardware peripherals and firmware without expending resources to "reinvent" microcontroller circuitry. Furthermore, much of the value of the phyCORE® module lies in its layout and test.

Production-ready Board Support Packages (BSPs) and Design Services for our hardware will further reduce development time and risk and allows for increased focus on product expertise. Take advantage of PHYTEC products to shorten time-to-market, reduce development costs, and avoid substantial design issues and risks. With this new innovative full system solution, new ideas can be brought to market in the most timely and cost-efficient manner.

For more information go to:

http://www.phytec.de/de/leistungen/entwicklungsunterstuetzung.html

or

http://www.phytec.eu/europe/oem-integration/evaluation-start-up.html

Ordering Information

The part numbering of the phyCORE has the following structure:

Product Specific Information and Technical Support

In order to receive product-specific information on all future changes and updates, we recommend registering at:

http://www.phytec.de/de/support/registrierung.html or http://www.phytec.eu/europe/support/registration.html

For technical support and additional information concerning your product, please visit the support section of our website which provides product-specific information, such as errata sheets, application notes, FAQs, etc.

https://www.phytec.de/produkt/system-on-modules/phycore-imx-8m-mini-nano/

or

https://www.phytec.eu/product-eu/system-on-modules/phycore-imx-8m-mini-nano/

Note

Assembly Options include a choice of Controller, RAM (Size/Type), Size of NAND Flash, interfaces available, vanishing, temperature range, as well as other features. Please contact our sales team to get more information on the ordering options available.

Declaration of Electro Magnetic Conformity of the PHYTEC phyCORE®‑i.MX 8M Mini

PHYTEC System on Module (henceforth products) are designed for installation in electrical appliances or as dedicated Evaluation Boards (i.e.: for use as a test and prototype platform for hardware/software development) in laboratory environments.

Warning

PHYTEC products lacking protective enclosures are subject to damage by ESD and, therefore, must be unpacked, handled, or operated in environments in which sufficient precautionary measures have been taken in respect to ESD-dangers. Only appropriately trained personnel such as qualified electricians, technicians, and engineers should handle and/or operate these products. Moreover, PHYTEC products should not be operated without protection circuitry if connections to the product's pin header rows are longer than 3 m.

PHYTEC products fulfill the norms of the European Union’s Directive for Electro Magnetic Conformity in accordance with the descriptions and rules of usage indicated in this hardware manual (particularly in respect to the pin header row connectors, power connector, and serial interface to a host-PC).

Tip

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of PHYTEC products, is subject to renewed establishment of conformity to and certification of Electro Magnetic Directives. Users should ensure conformance following any modifications to the products as well as the implementation of the products into target systems.

Product Change Management and Information Regarding Parts Populated on the SOM / SBC

With the purchase of a PHYTEC SOM / SBC you will, in addition to our hardware and software possibilities, receive free obsolescence maintenance service for the hardware we provide. Our PCM (Product Change Management) team of developers is continuously processing all incoming PCN's (Product Change Notifications) from vendors and distributors concerning parts that are used in our products. Possible impacts on the functionality of our products due to changes in functionality or obsolesce of certain parts are constantly being evaluated in order to take the right measures either in purchasing decisions or within our hardware/software design.

Our general philosophy here is: We never discontinue a product as long as there is a demand for it.

Therefore, we have established a set of methods to fulfill our philosophy:

Avoidance strategies:

- Avoid changes by evaluating the longevity of parts during the design-in phase.

- Ensure the availability of equivalent second source parts.

- Stay in close contact with part vendors to be aware of roadmap strategies.

Change management in the rare event of an obsolete and non-replaceable part:

- Ensure long-term availability by stocking parts through last time buy management according to product forecasts.

- Offer long-term frame contracts to customers.

Change management in case of functional changes:

- Avoid impacts on product functionality by choosing equivalent replacement parts.

- Avoid impacts on product functionality by compensating changes through hardware redesign or backward-compatible software maintenance.

- Provide early change notifications concerning functional, relevant changes to our products.

We refrain from providing detailed part-specific information within this manual, which can be subject to continuous changes, due to part maintenance for our products.

In order to receive reliable, up-to-date, and detailed information concerning parts used for our product, please contact our support team through the contact information given within this manual.

PHYTEC Documentation

PHYTEC will provide a variety of hardware and software documentation for all of our products. This includes any or all of the following:

- Quickstart Guide: A short guide on how to set up and boot a phyCORE board along with brief information on building a BSP, the device tree, and accessing peripherals.

- Hardware Manual: A detailed description of the System on Module and accompanying carrier board.

- Yocto Guide: A comprehensive guide for the Yocto version the phyCORE uses. This guide contains an overview of Yocto; an introduction, installing and customizing the PHYTEC BSP; how to work with programs like Poky and Bitbake; and much more.

- BSP Manual: A manual specific to the BSP version of the phyCORE. Information such as how to build the BSP, booting, updating software, device tree, and accessing peripherals can be found here.

- Development Environment Guide: This guide shows how to work with the Virtual Machine (VM) Host PHYTEC has developed and prepared to run various Development Environments. There are detailed step-by-step instructions for Eclipse and Qt Creator, which are included in the VM. There are instructions for running demo projects for these programs on a phyCORE product as well. Information on how to build a Linux host PC yourself is also a part of this guide.

- Pin Muxing Table: phyCORE SOMs have an accompanying pin table (in Excel format). This table will show the complete default signal path, from processor to carrier board. The default device tree muxing option will also be included. This gives a developer all the information needed in one location to make muxing changes and design options when developing a specialized carrier board or adapting a PHYTEC phyCORE SOM to an application.

On top of these standard manuals and guides, PHYTEC will also provide Product Change Notifications, Application Notes, and Technical Notes. These will be done on a case-by-case basis. Most of the documentation can be found in the applicable download page of our products.

Tip

After finishing the Quickstart Guide, we recommend working through the Development Environment Guide. This will give you a comprehensive overview of the features and functions of both the SOM and carrier board.

phyCORE‑i.MX 8M Mini Introduction

The phyCORE‑i.MX 8M Mini belongs to PHYTEC’s phyCORE System on Module family. The phyCORE SOMs represent the continuous development of PHYTEC System on Module technology. Like its mini-, micro-, and nanoMODUL predecessors, phyCORE boards integrate all core elements of a microcontroller system on a sub-miniature board and are designed in a manner that ensures their easy expansion and embedding in peripheral hardware developments.

Independent research indicates approximately 70 % of all EMI (Electro-Magnetic Interference) problems are caused by insufficient supply voltage grounding of electronic components in high-frequency environments. The phyCORE board design features an increased pin package, which allows for the dedication of approximately 37 % of all connector pinson the phyCORE boards to Ground. This improves EMI and EMC characteristics and makes it easier to design complex applications meeting EMI and EMC guidelines using phyCORE boards, even in high noise environments.

phyCORE boards achieve their small size through modern SMT and multi-layer design. Due to the complexity of our modules, 0201-packaged SMT components and laser-drilled microvias are used on the boards, providing phyCORE users with access to this cutting-edge miniaturization technology for integration into their own design.

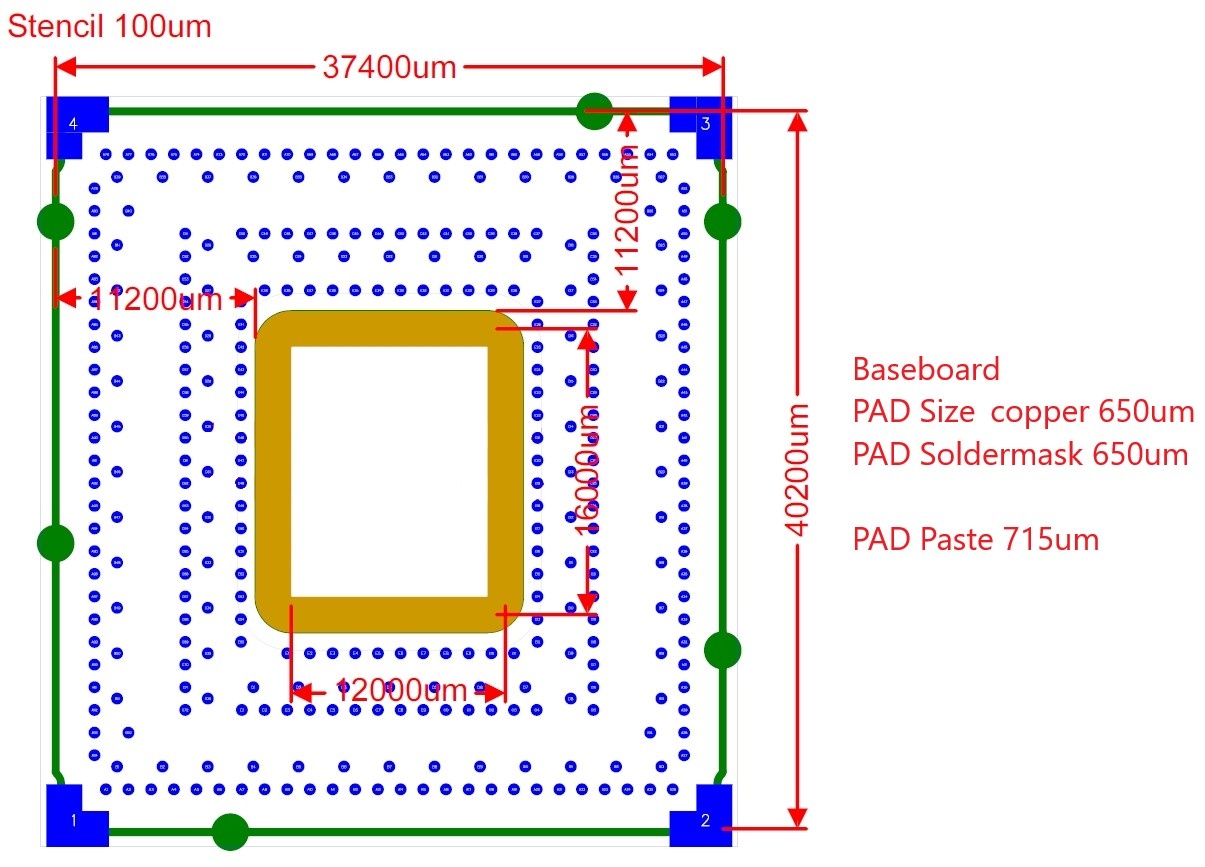

The phyCORE‑i.MX 8M Mini is a sub-miniature (37 mm x 40 mm) soldered System on Module populated with the NXP® Semiconductor i.MX 8M Mini microcontroller. Its universal design enables its insertion in a wide range of embedded applications. All controller signals and ports extend from the controller to a 1,27mm pitch BGA Ball. Each signal ball has an associated GND pin which ensures the GND reference for each signal. The ball packages are placed in lines. There is enough space between lines to ensure the possibility of easy routing out of the package. Signal balls for a high-speed signal like HDMI are placed on the outer lines, making it easy to route to the top layer of the carrier board. The SOM is designed to support carrier boards with as little as 6 layers to reduce PCB costs. For proper EMC characteristics, it is necessary to place the processor caps directly under the SOM. This required a hole in the carrier board.

The descriptions in this manual are based on the NXP® Semiconductor i.MX 8M Mini. Descriptions of compatible microcontroller derivative functions are not included, as such functions are not relevant for the basic functioning of the phyCORE‑i.MX 8M Mini.

phyCORE‑i.MX 8M Mini Features

The phyCORE‑i.MX 8M Mini offers the following features:

- Insert-ready, sub-miniature (37 mm x 40 mm) System on Module (SOM) sub-assembly in low EMI design, achieved through advanced SMD technology

- Mounted using BGA Technology

- Populated with the NXP® Semiconductor i.MX 8M Mini microcontroller (BGA486 packaging)

- 1.6 GHz core clock frequency (up to 1.8 GHz)

- Boot from different memory devices (eMMC standard)

- Single supply voltage of +3.3 V with onboard power management

- All controller required supplies are generated onboard

- Improved interference safety achieved through multi-layer PCB technology and dedicated ground pins

2 GB (up to 4 GB[1]) LPDDR4 RAM

- 4 GB (up to 32 GB[1]) onboard eMMC

- 4 kB[1] I2C EEPROM

- Two High-Speed USB 2.0 OTG interfaces

One 10/100/1000 MBit Ethernet interface (if Ethernet transceiver is mounted)[2]

- One RGMII interface at TTL level (if Ethernet transceiver is not mounted)[2]

- Three I2C interfaces

- Two SPI interfaces

- One PCIe interface

- Four UART interfaces

- Four PWM outputs

- One LVDS interface (if MIPI-DSI to LVDS converter is mounted)[2]

- One MIPI DSI interface (if MIPI-DSI to LVDS converter is not mounted)[2]

- One MIPI CSI camera interface

- One 4-Bit SD-Card interface

- One 8-Bit SDIO interface

- SAI audio interface

- Internal RTC

- Available for different temperature grades (Product Temperature Grades)

| 1. | 123 The maximum memory size listed as of the printing of this manual. Please contact PHYTEC for more information about additional or new module configurations available. |

| 2. | 1234 Please refer to the order options described in the Preface or contact PHYTEC for more information about additional module configurations. |

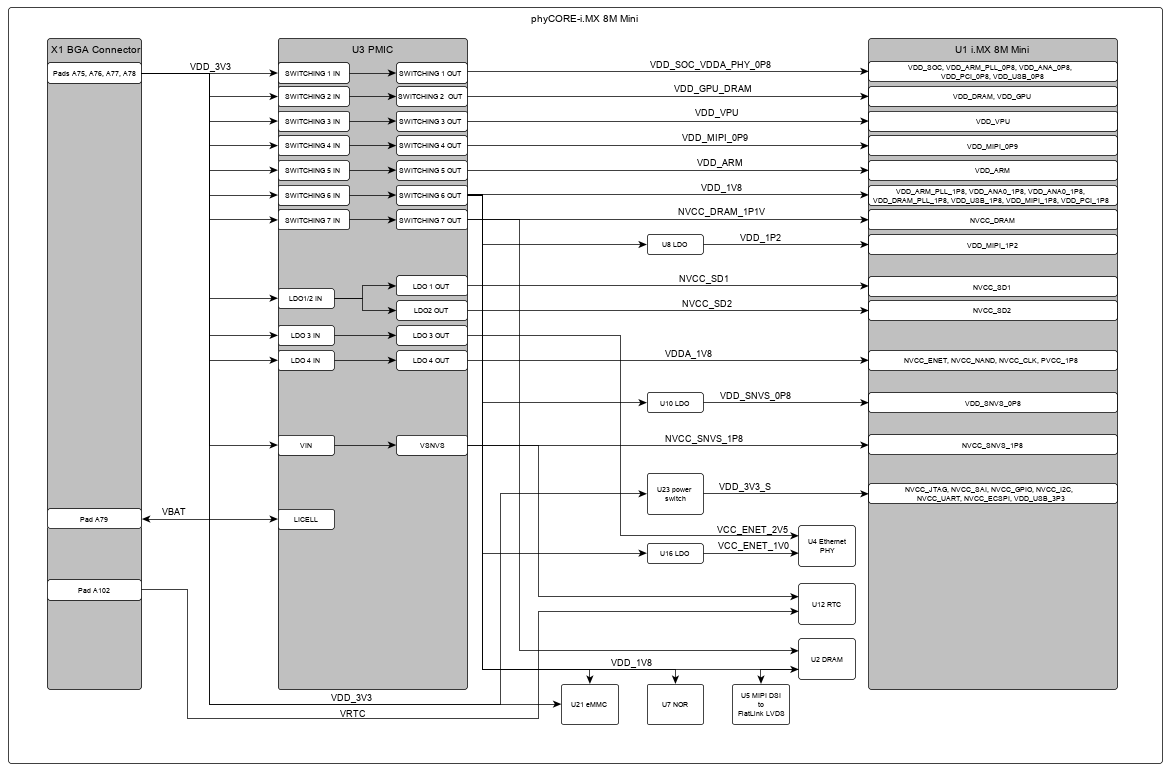

phyCORE-i.MX 8M Mini Block Diagram

phyCORE-i.MX 8M Mini Block Diagram

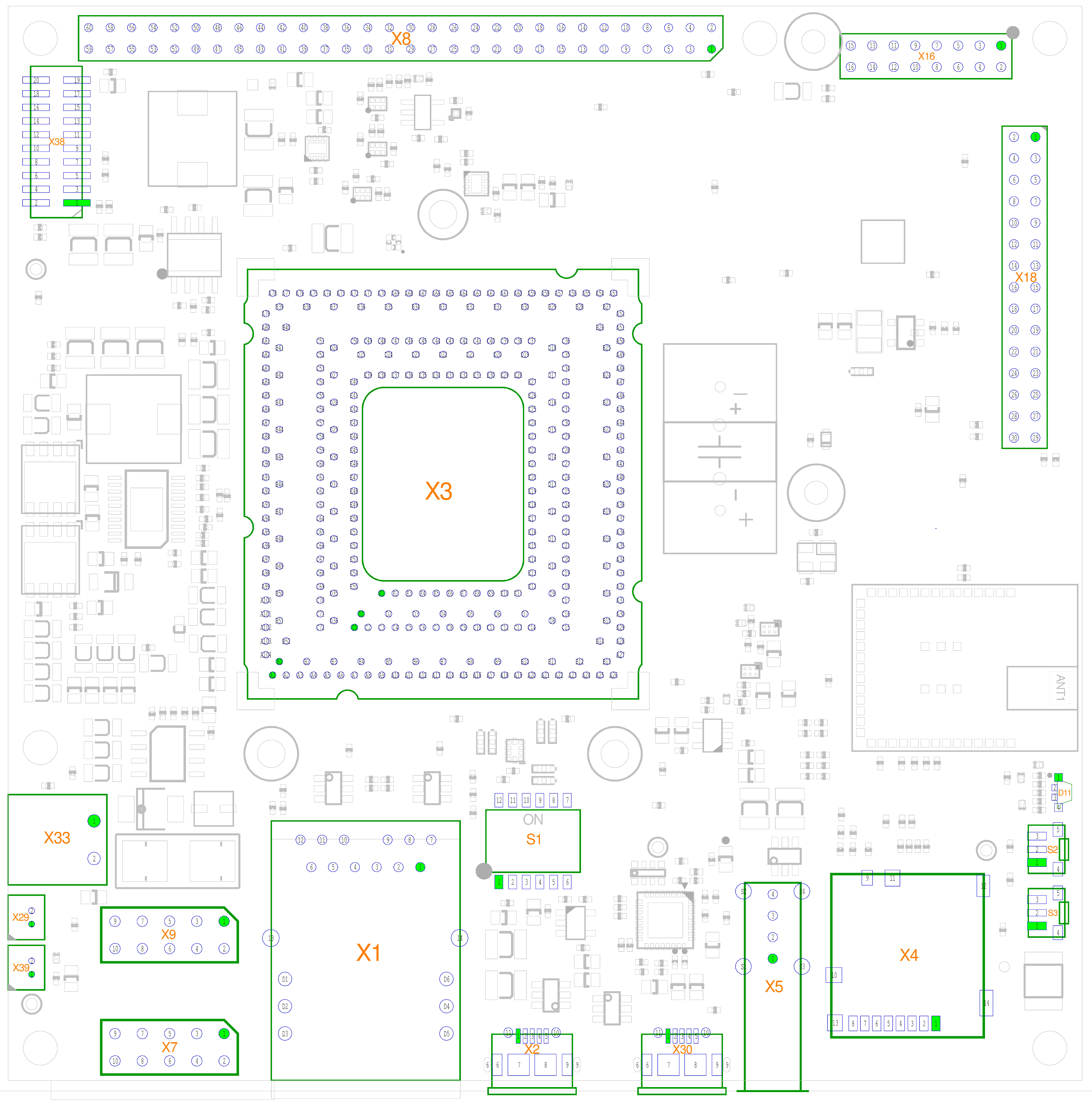

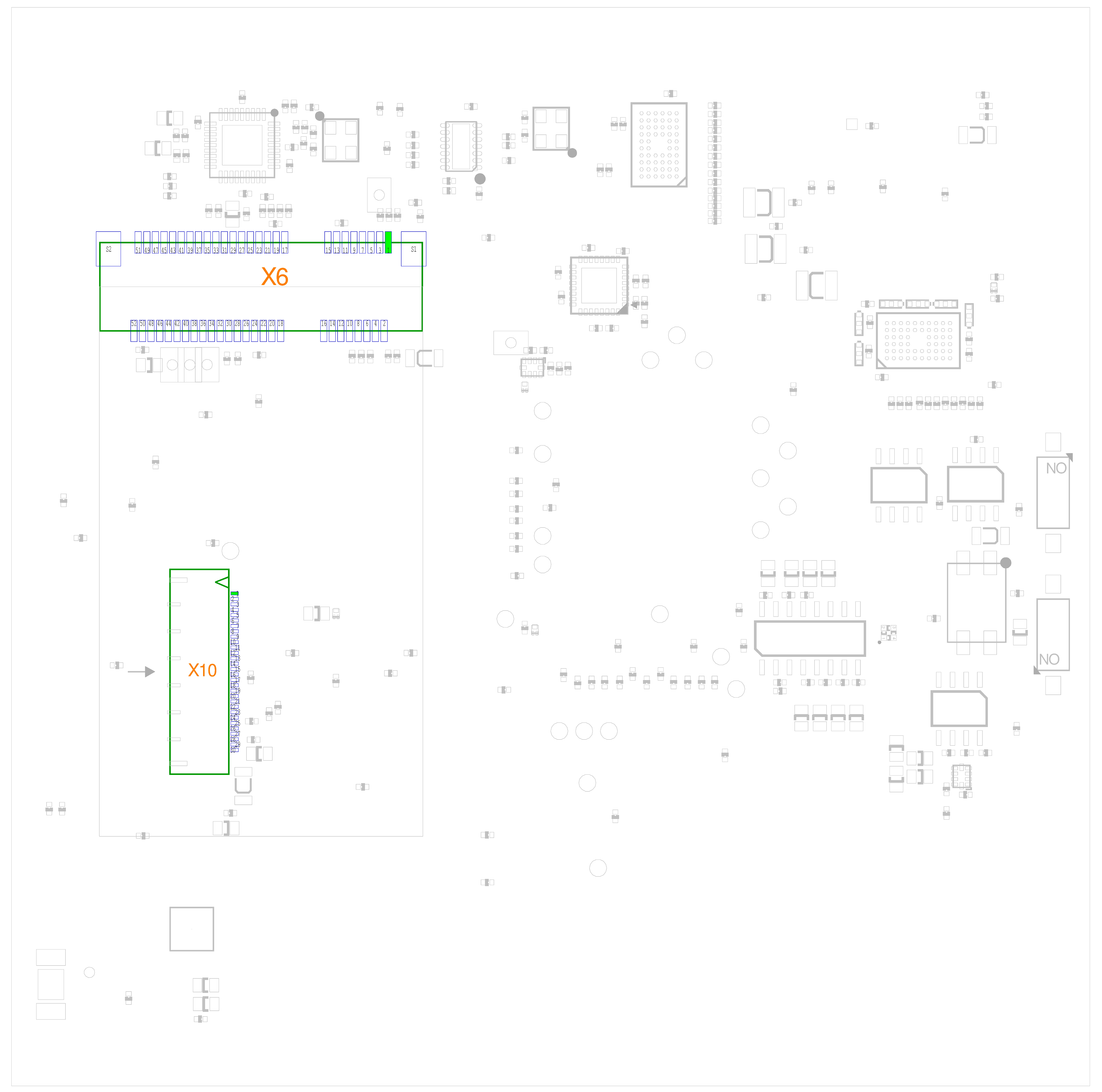

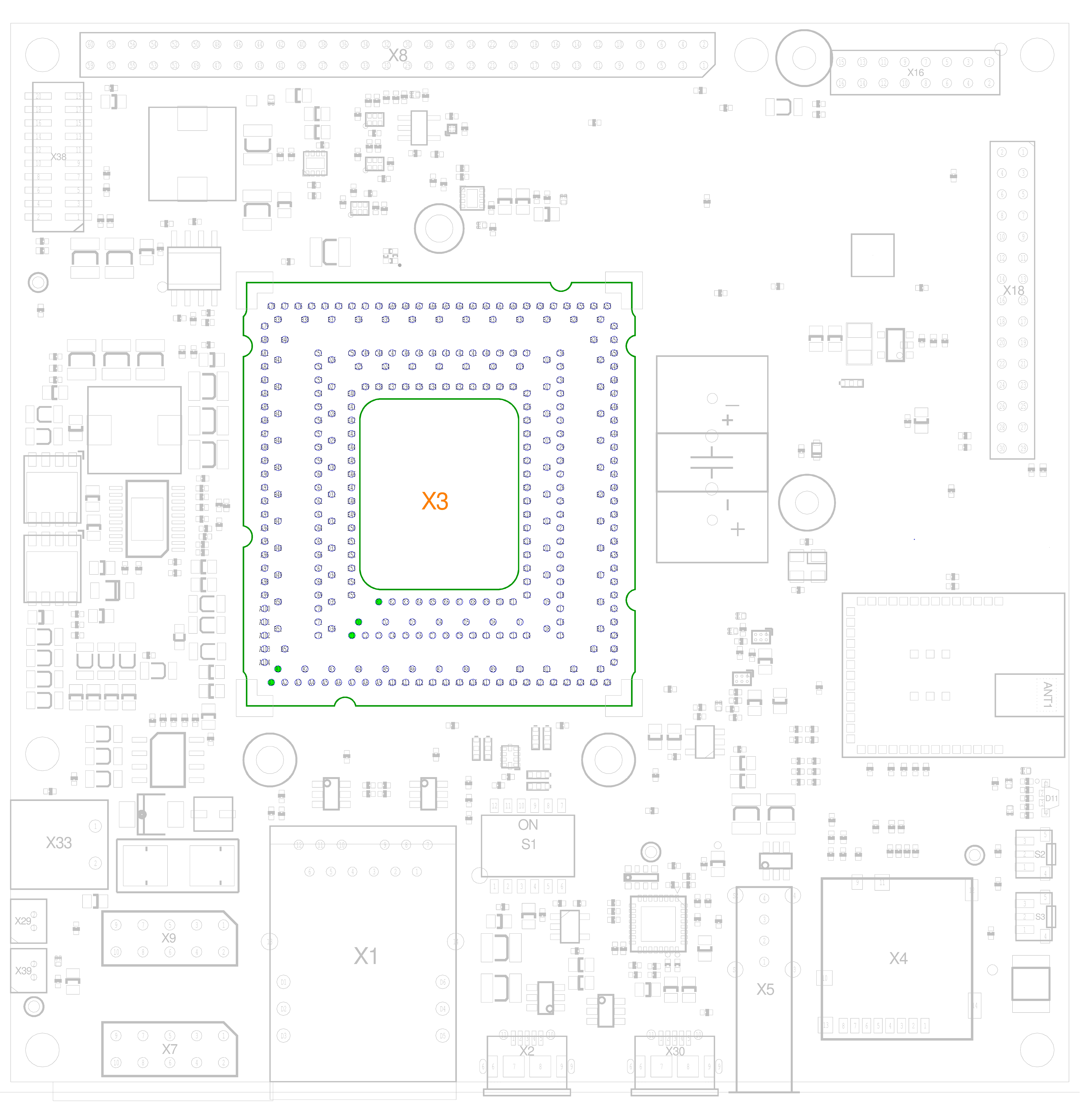

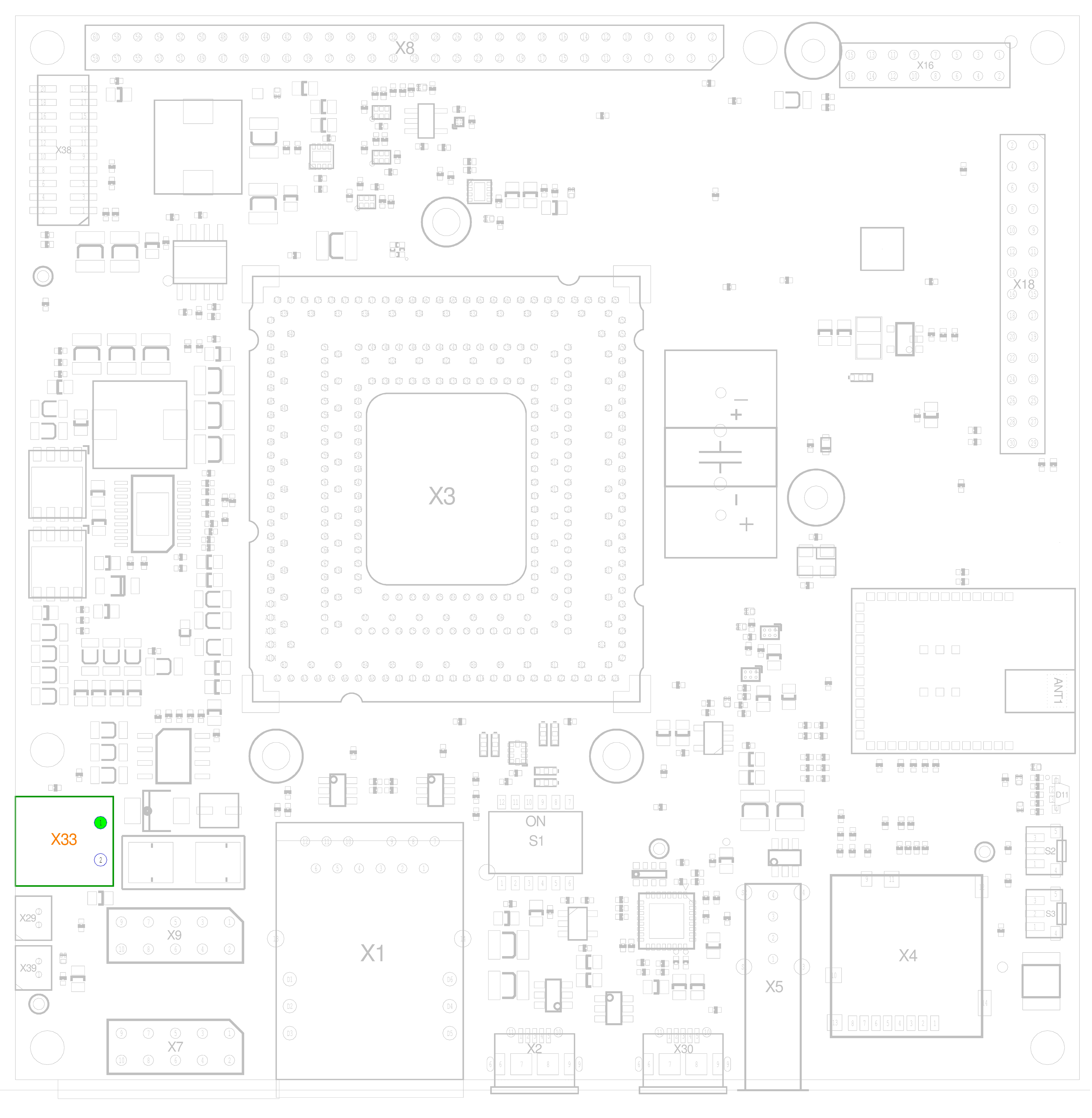

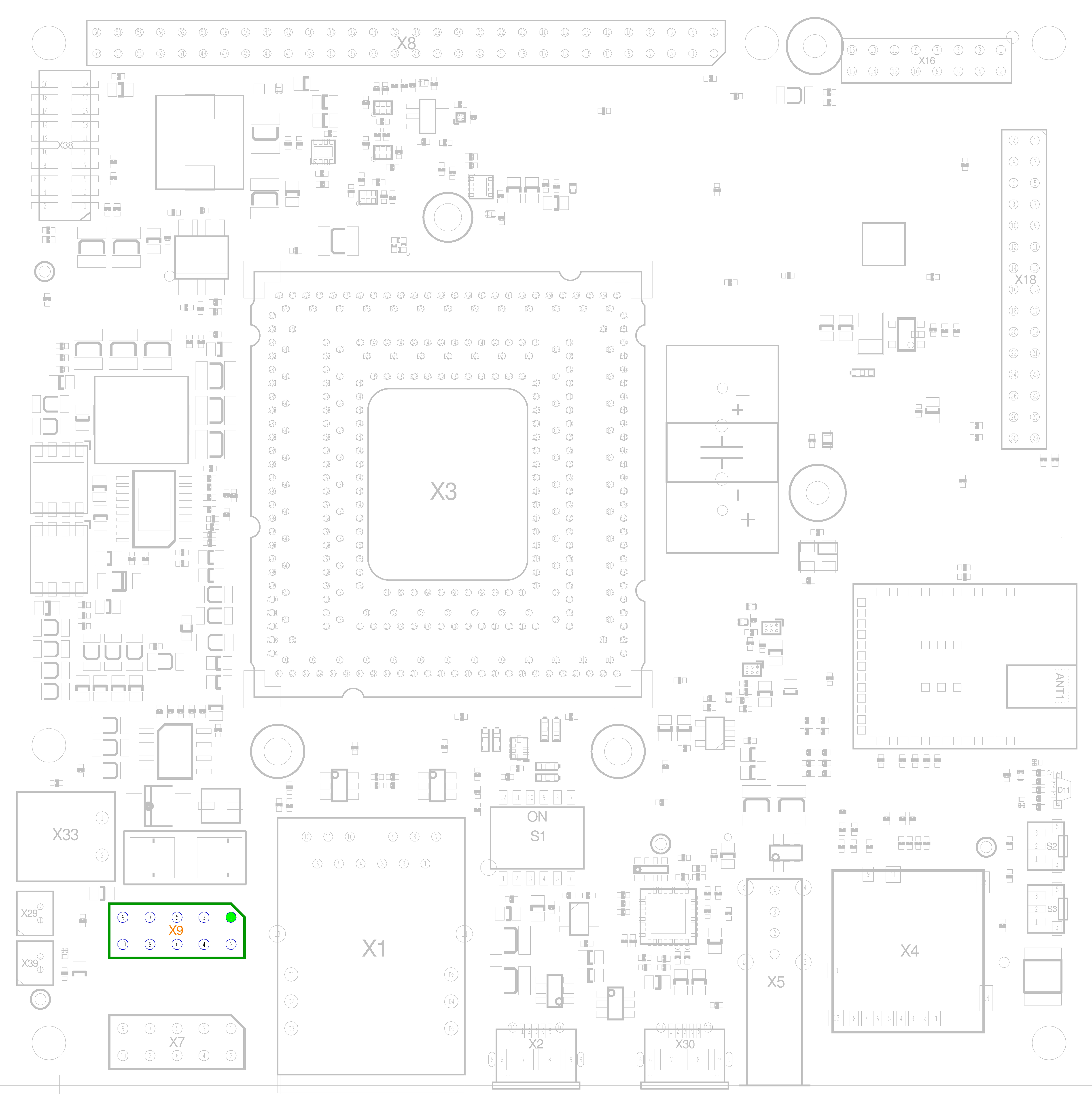

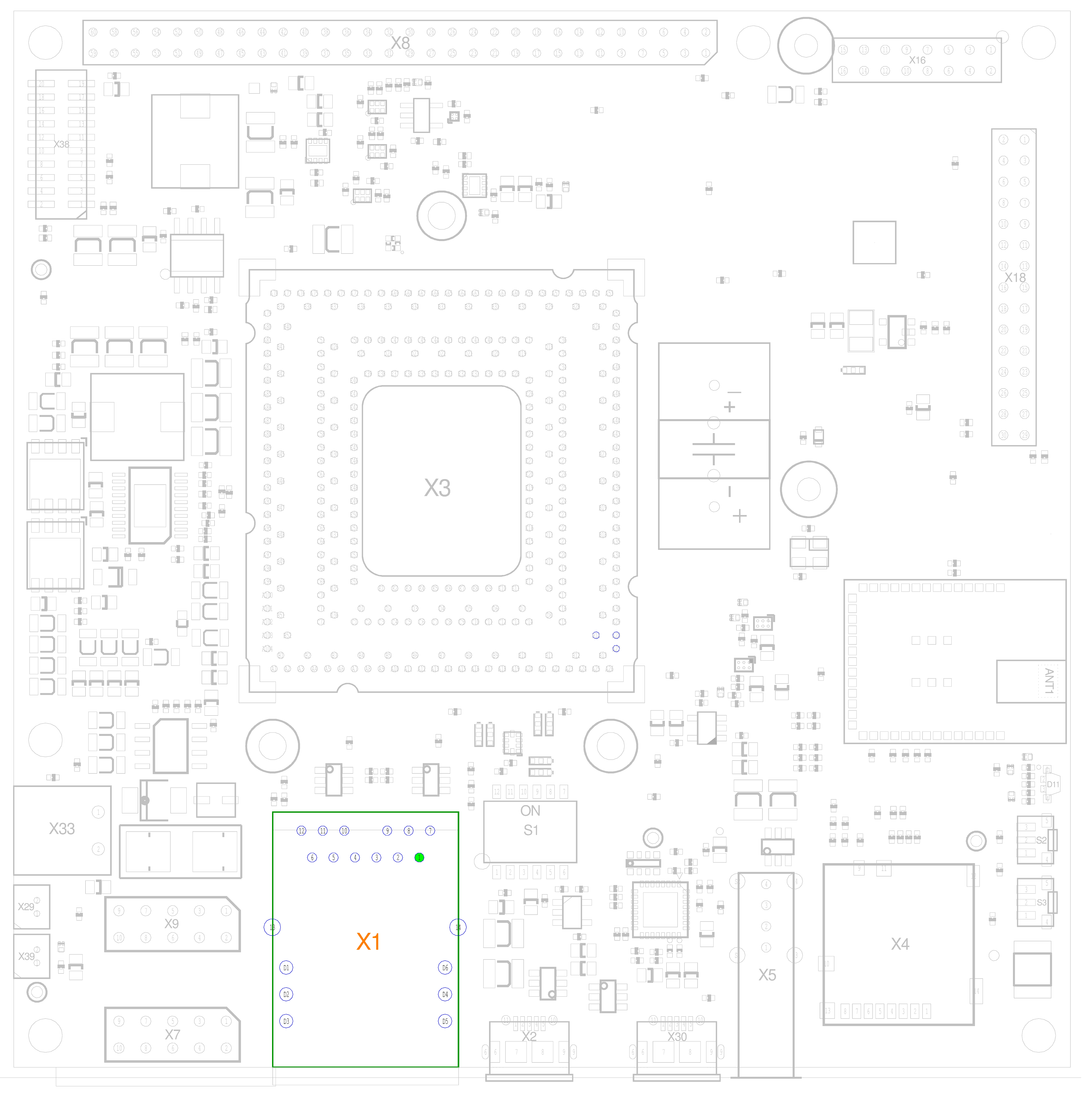

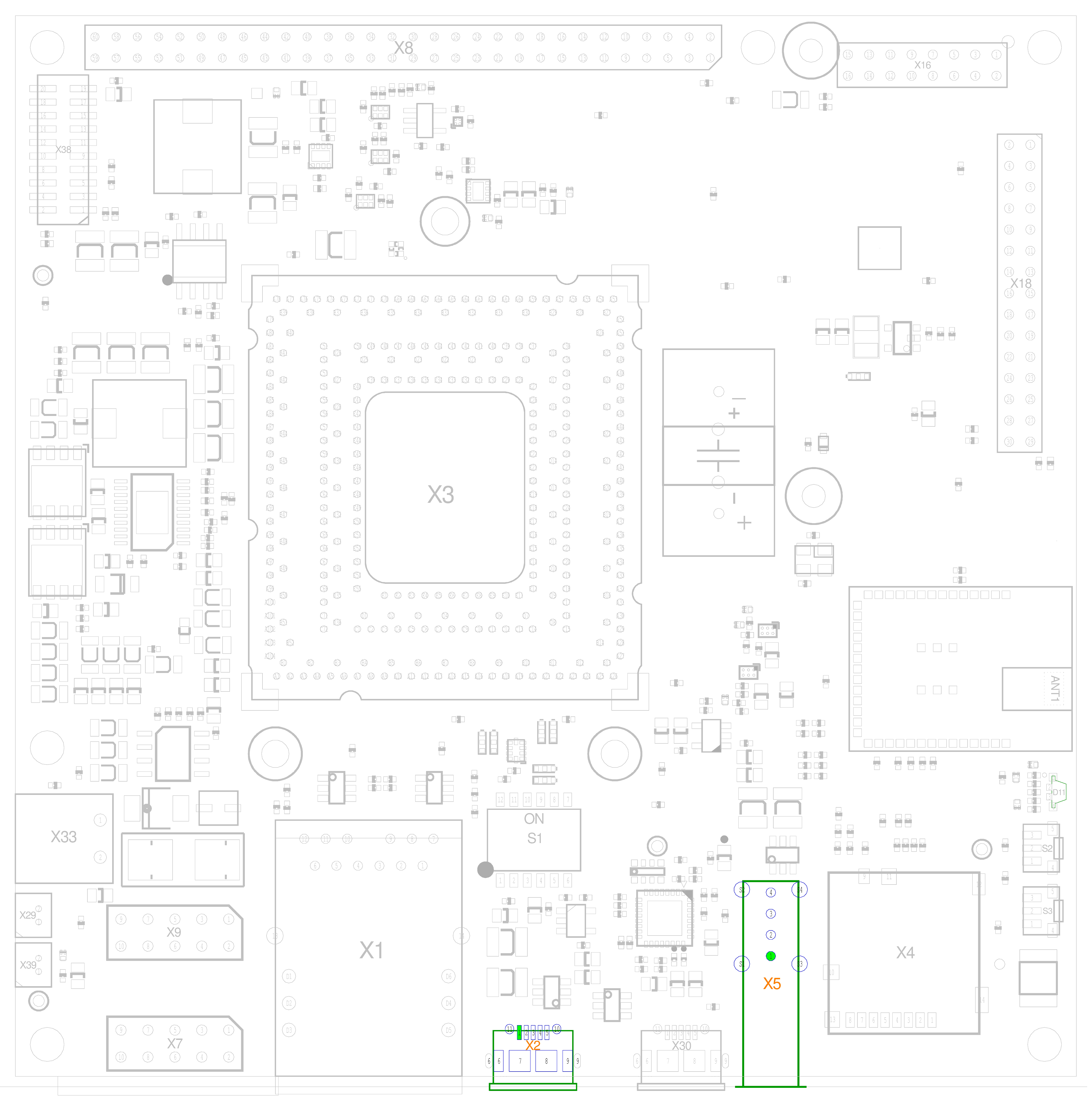

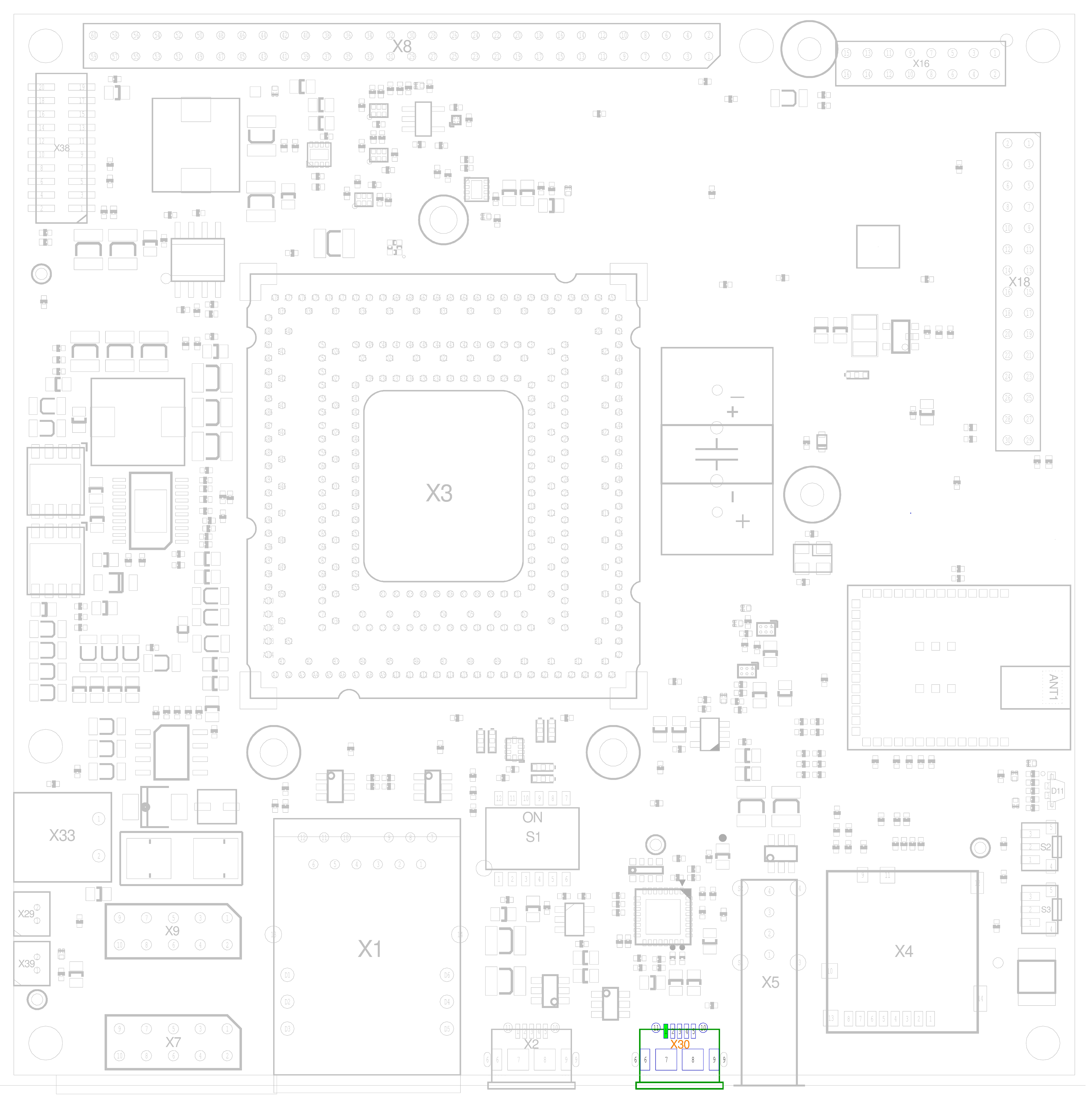

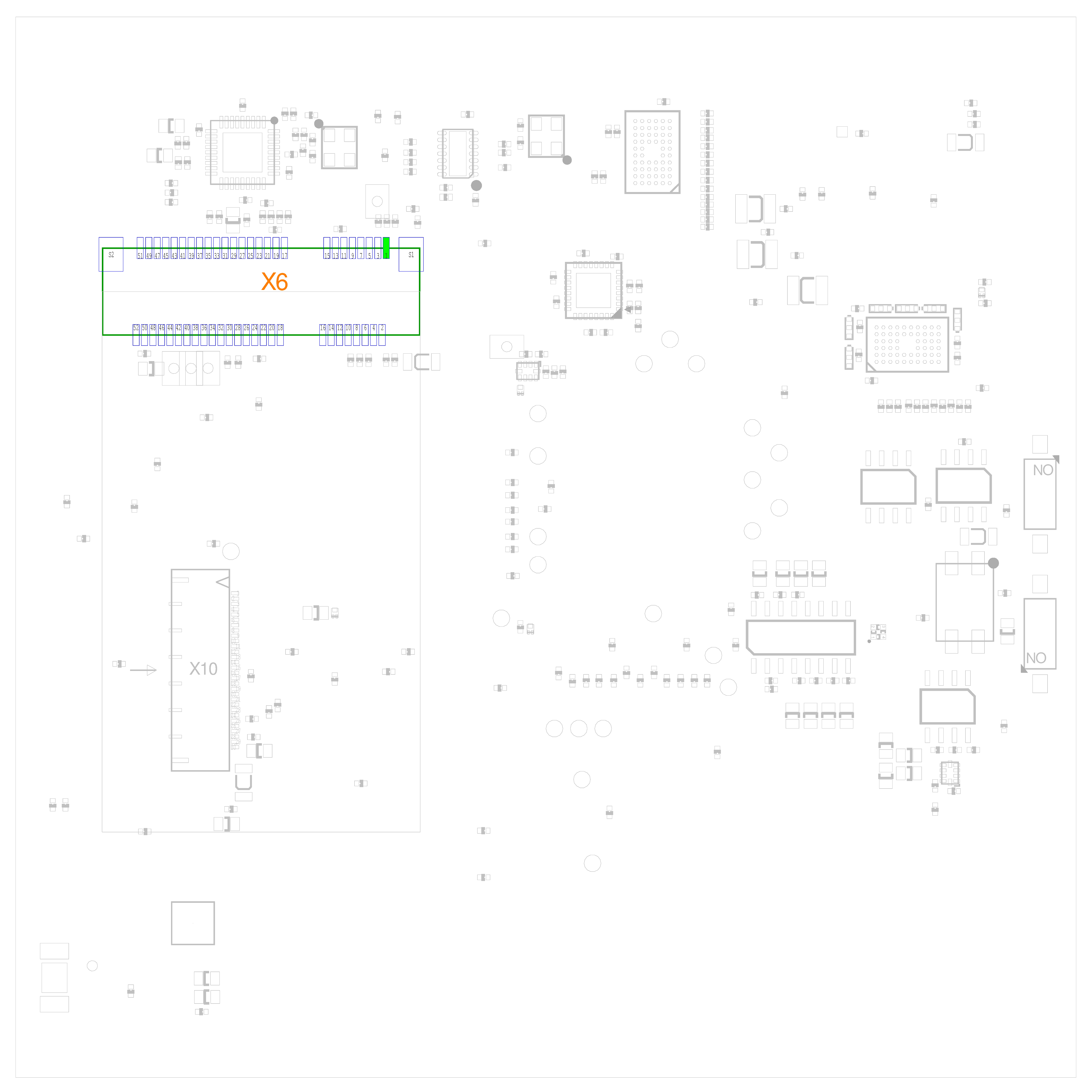

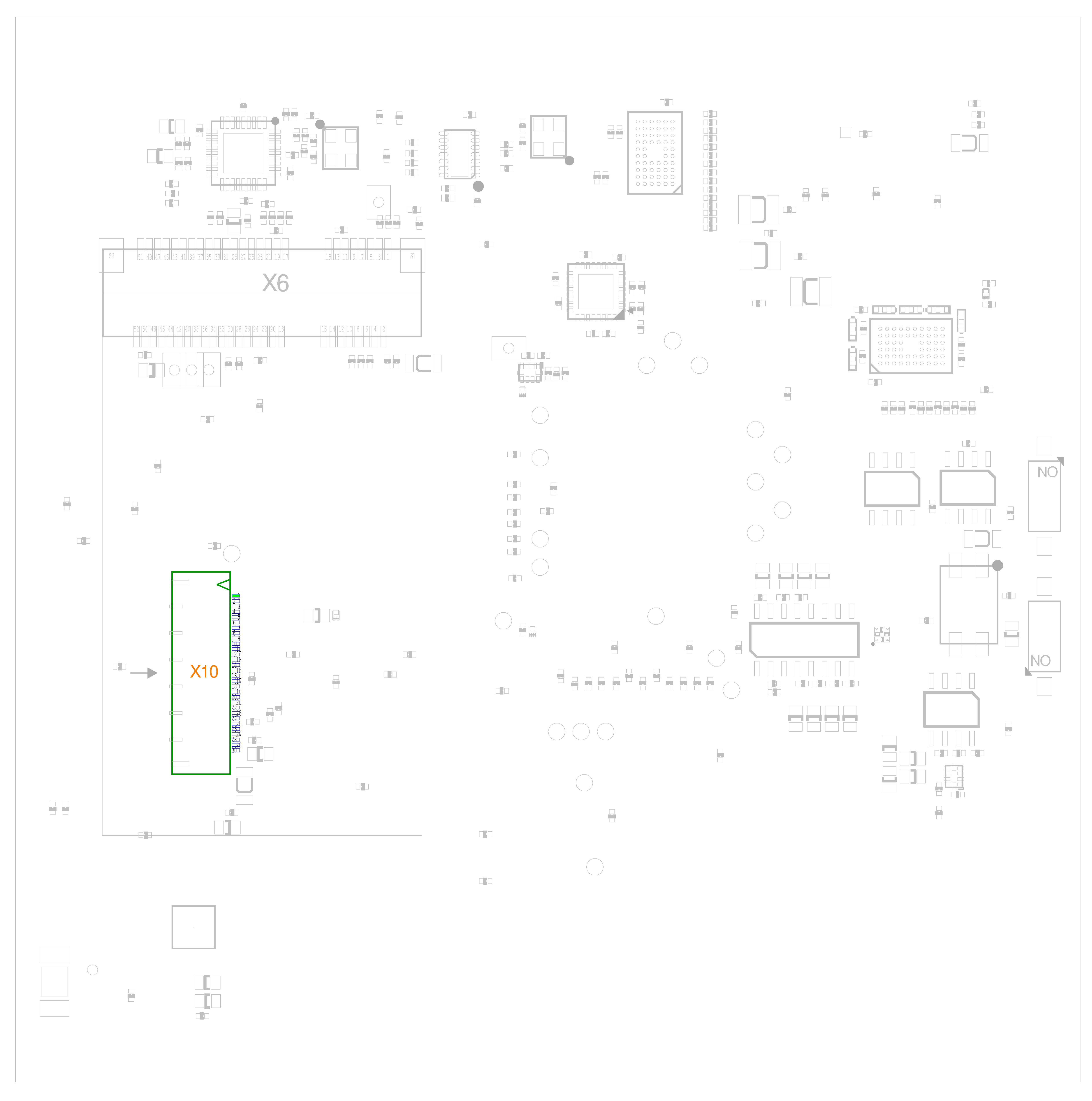

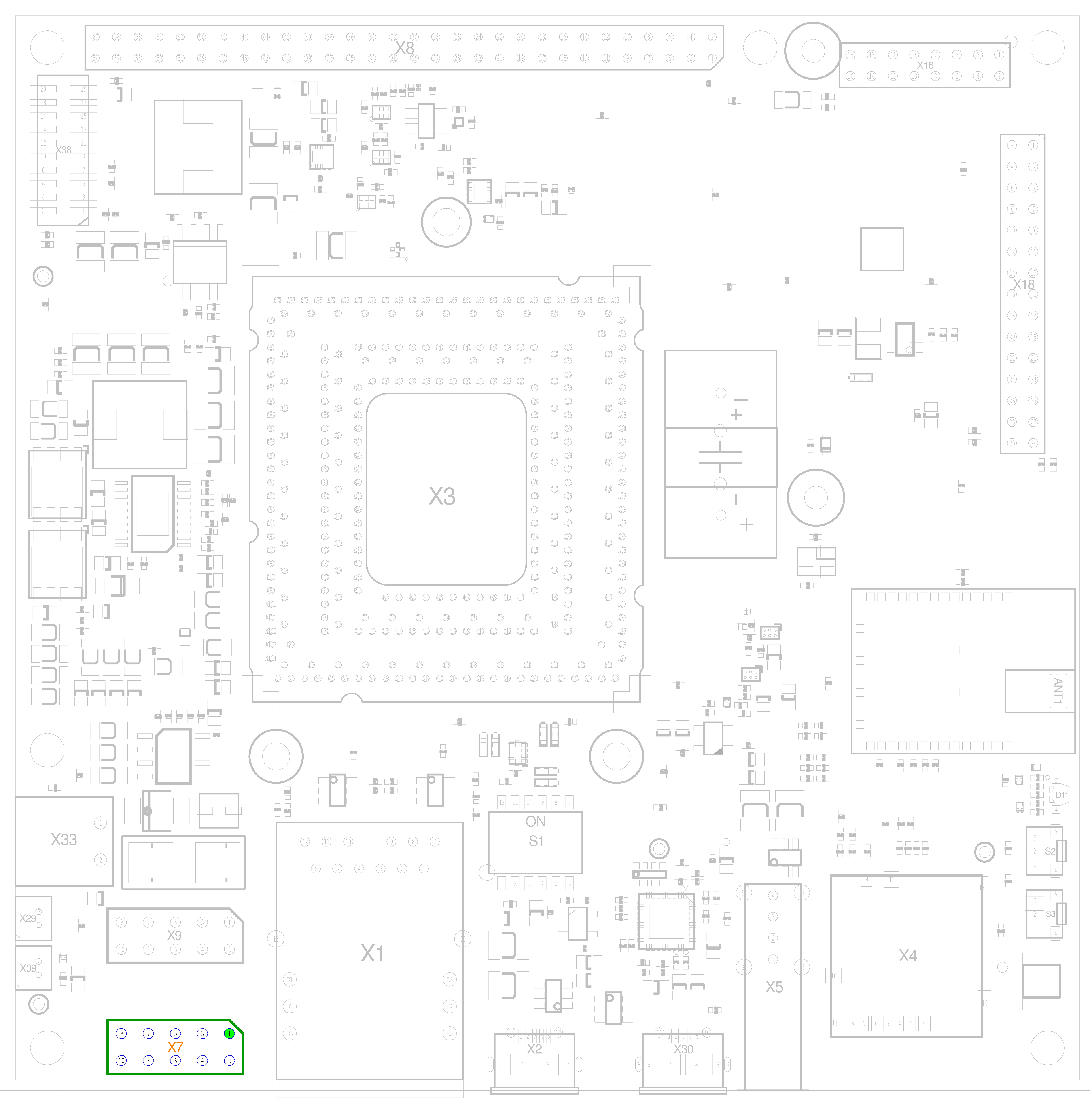

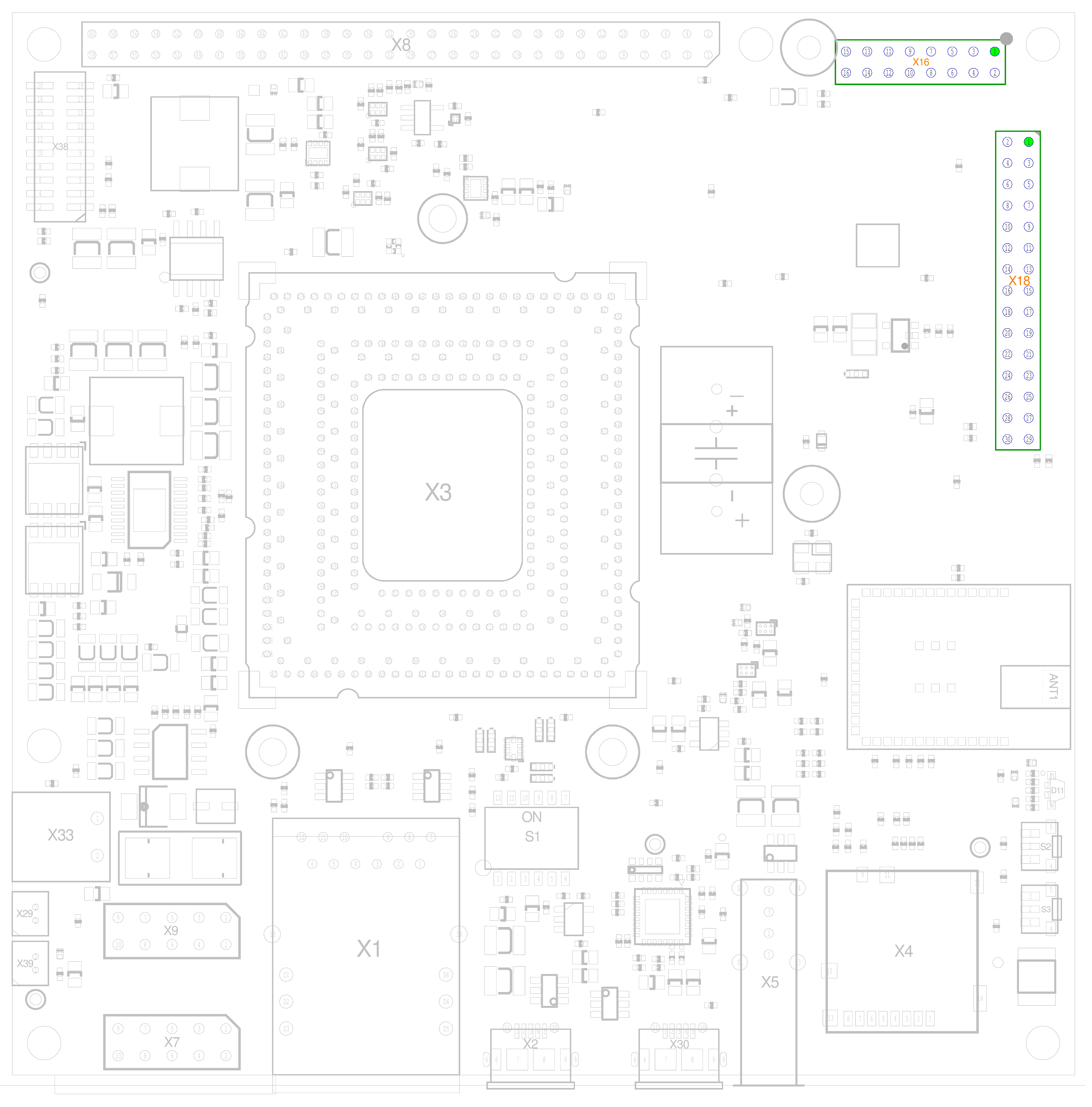

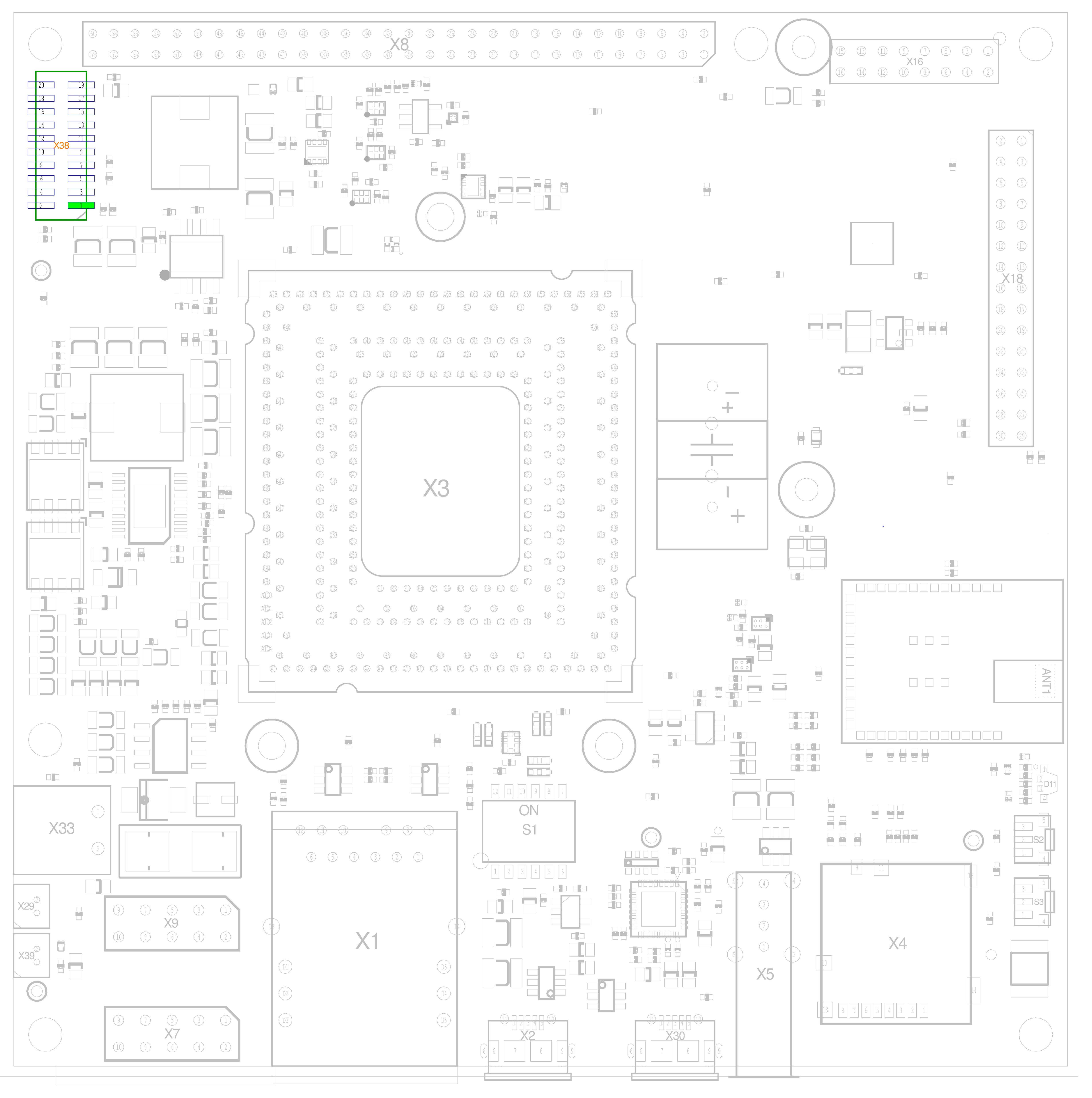

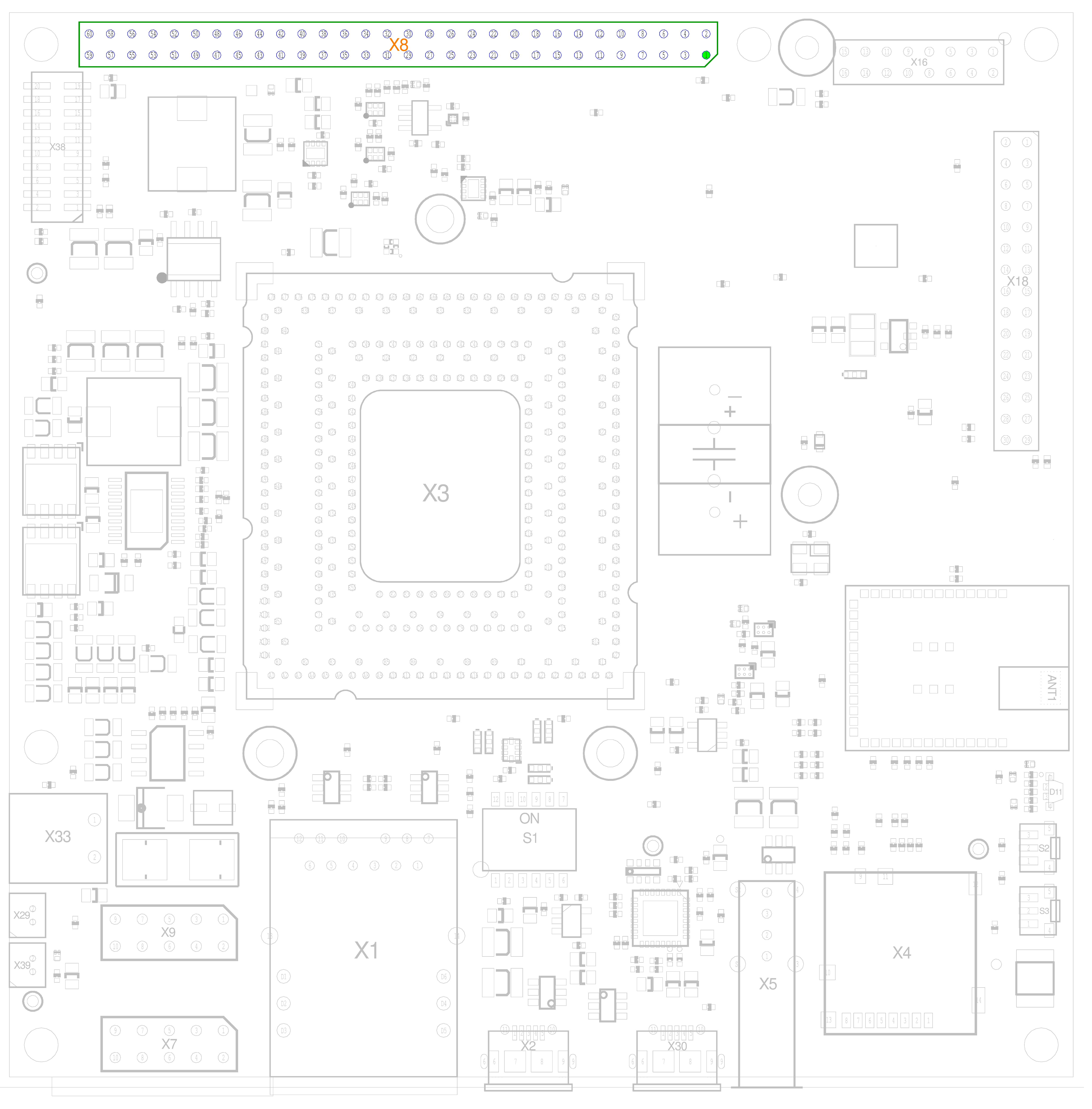

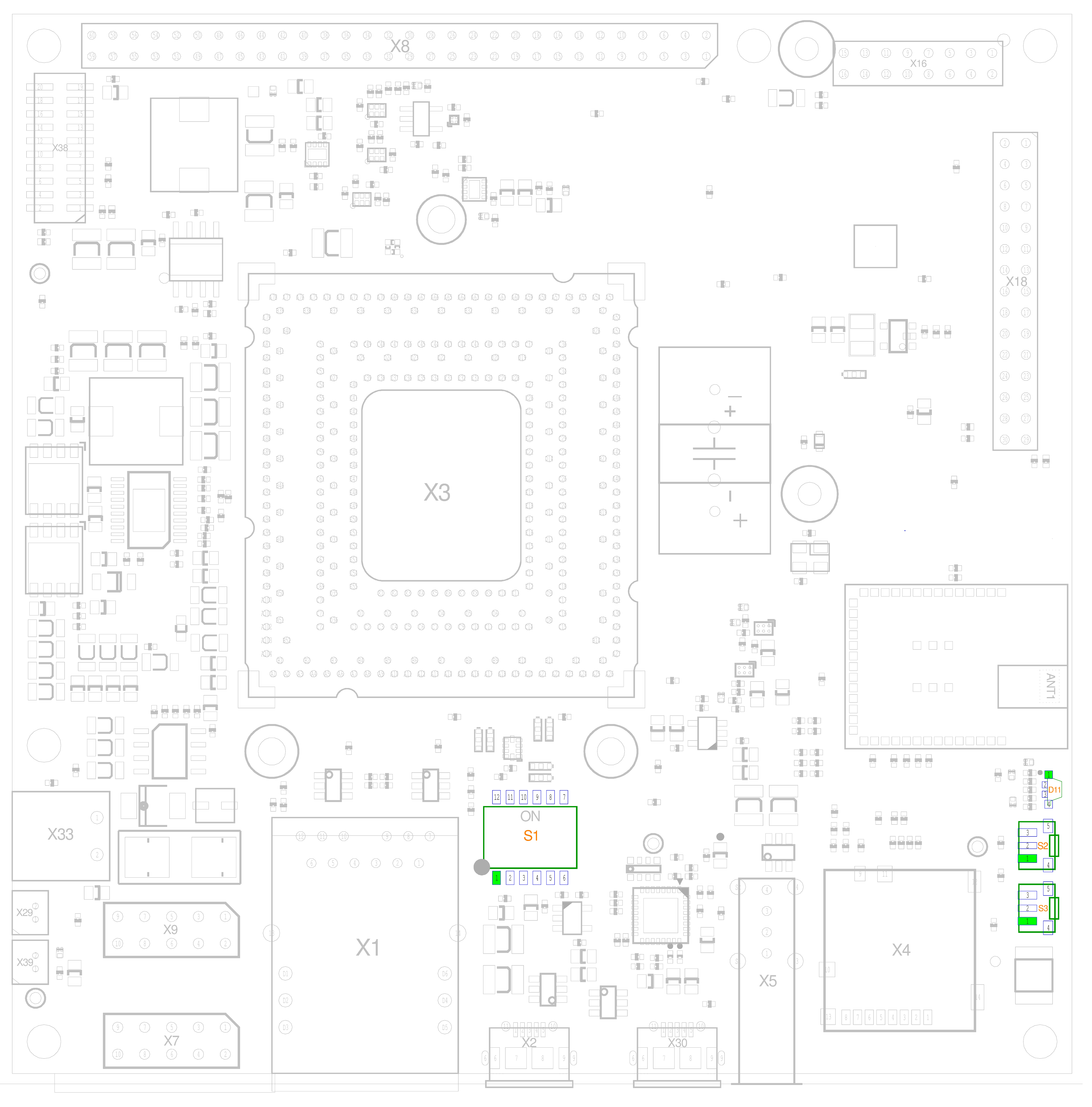

phyCORE-i.MX 8M Mini Component Placement

phyCORE-i.MX 8M Mini Component Placement (Top)

phyCORE-i.MX 8M Mini Component Placement (Bottom)

phyCORE-i.MX 8M Mini Minimal Operating Requirements

We recommend connecting all available VDD_3V3 input pins to the power supply system on a custom carrier board housing the phyCORE-i.MX 8M Mini and, at minimum, the matching number of GND pins neighboring the VDD_3V3 input pins. In addition, proper implementation of the phyCORE-i.MX 8M Mini module into a target application also requires connecting all GND pins.

Refer to Power for more information.

Pin Description

Module connections must not exceed their expressed maximum voltage or current. Maximum signal input values are indicated in the corresponding controller manuals/datasheets. As damage from improper connections varies according to use and application, it is the user's responsibility to take appropriate safety measures to ensure that the module connections are protected from overloading through connected peripherals.

All controller signals extend to BGA Signal Balls (1.27 mm) which allows the phyCORE‑i.MX 8M Mini to be soldered into any target application like a "big chip".

PHYTEC provides a complete pinout table for the phyCORE-i.MX 8M Mini Connector X1. This table contains a complete signal path for the phyCORE‑i.MX 8M Mini and the carrier board phyBOARD-Polis, including signal names, pin muxing paths, and descriptions specific to each pin. It also provides the appropriate voltage domain, signal type (ST), and a functional grouping of the signals. The signal type also includes information about the signal direction. A table describing the signal types can be found with the pinout table.

Warning

- The NXP® Semiconductor i.MX 8M Mini is a multi-voltage-operated microcontroller and, as such, special attention should be paid to the interface voltage levels to avoid unintentional damage to the microcontroller and other onboard components. Please refer to the NXP Semiconductor NXP i.MX 8M Mini Reference Manual for details on the functions and features of controller signals and port pins.

- As some of the signals which are brought out on the phyCORE-Connector are used to configure the boot mode for specific boot options, please make sure that these signals are not driven by any device on the baseboard during reset. The signals which may affect the boot configuration are shown in the table phyCORE-Connector Boot Configuration Pins.

- It is necessary to avoid voltages at the IO pins of the phyCORE-i.MX 8M Mini which are sourced from the supply voltage of peripheral devices attached to the SOM during power-up or power–down. These voltages can cause a current flow into the controller, especially if peripheral devices attached to the interfaces of the i.MX 8M Mini are supposed to be powered while the phyCORE‑i.MX 8M Mini is in suspend mode or turned off. To avoid this, bus switches either supplied by VDD_3V3_S on the phyCORE side or having their output enabled to the SOM controlled by the X_PGOOD_OD signal (see External Logic Supply Voltage) must be used.

Tips

- Most of the controller pins have multiple multiplexed functions. As most of these pins are connected directly to the phyCORE-Connector, the alternative functions are available by using the i.MX 8M's pin muxing options. Signal names and descriptions in the accompanying table, however, are in regard to the specification of the phyCORE‑i.MX 8M and the functions defined. Please refer to the i.MX8M Reference Manual or the schematic to get to know about alternative functions. In order to utilize a specific pin's alternative function, the corresponding registers must be configured within the appropriate driver of the BSP.

- The following tables describe the full set of signals available at the phyCORE‑Connector according to the phyCORE-i.MX 8M specification. However, the availability of some interfaces is order-specific (e.g. Camera_0). Thus, some signals might not be available on your module.

- As the phyCORE-i.MX 8M Mini is delivered with the carrier board phyBOARD‑Polis, the pin muxing might be changed within the appropriate BSP in order to support all features of the carrier board. If so, information on the differences from the pinout given in the following tables can be found in the carrier board's documentation.

Unused Signals

It is recommended to handle unused signals according to the table below.

| Interface | Signals | Recommendation |

|---|---|---|

| MIPI-CSI | X_MIPI_CSI_CLK_N X_MIPI_CSI_CLK_P X_MIPI_CSI_DATA0_N X_MIPI_CSI_DATA0_P X_MIPI_CSI_DATA1_N X_MIPI_CSI_DATA1_P X_MIPI_CSI_DATA2_N X_MIPI_CSI_DATA2_P X_MIPI_CSI_DATA3_N X_MIPI_CSI_DATA3_P | Connect to GND |

| MIPI-DSI/FlatLink-LVDS | X_FLATLINK_D0_N/MIPI_DSI_DATA0_N | Leave unconnected |

| PCIe | X_PCIe_CLK_N | Leave unconnected |

| USB1 | USB1_VBUS X_USB1_DN X_USB1_DP X_USB1_ID | Leave unconnected |

| USB2 | USB2_VBUS X_USB2_DN X_USB2_DP X_USB2_ID | Leave unconnected |

| ETHERNET | X_ETH_A_P X_ETH_A_N X_ETH_B_P X_ETH_B_N X_ETH_C_P X_ETH_C_N X_ETH_D_P X_ETH_D_N | Leave unconnected |

| GPIO | All remaining single-ended signals | Leave unconnected |

Power

The phyCORE‑i.MX 8M Mini operates off of a single power supply voltage. The following sections discuss the primary power pins on the phyCORE-i.MX 8M Mini Connector X1 in detail.

Primary System Power (VDD_3V3)

The phyCORE‑i.MX 8M Mini operates with a single primary voltage supply. Onboard switching and low dropout regulators generate the 2.5 V, 1.8 V, 1.2 V, 1.1 V, 0.9 V, and 0.8 V voltage rails required by the i.MX 8M Mini CPU and onboard components from the input voltage VDD_3V3.

For proper operation, the phyCORE‑i.MX 8M Mini must be supplied with a voltage source of 3.3 V +4.5 %-4 % with 2 A load at the VDD pins on the phyCORE-i.MX 8M Mini Connector X1.

In order to perform a full power cycle of the phyCORE-i.MX 8M Mini, including the SNVS domain of the PMIC and the CPU, the voltage input rail VDD_3V3 has to remain below 0,3 V for at least 600 ms.

Note

It is recommended to choose a slightly higher value than 3.3 V for VDD_3V3 in order to account for series resistance of 3.3 V load switching components on the SoM. The PHYTEC phyBOARD-Polis for example supplies VDD_3V3 with 3.366 V ±3.5 %.

VDD_3V3: X1 → A75, A76, A77, A78

Connect all VDD_3V3 input pins to your power supply and, at the very least, the matching number of GND pins.

Corresponding GND: X1 → B36, B37, B38, B39, B40, B41

Please refer to the section Pin Description for information on additional GND pins located at the phyCORE-i.MX 8M Mini Connector X1.

Warning

As a general design rule, PHYTEC recommends connecting all GND pins neighboring signals which are being used in the application circuitry. For maximum EMI performance, all GND pins should be connected to a solid ground plane.

Power Management IC (PMIC)(U3)

The phyCORE-i.MX 8M Mini provides an onboard Power Management IC (PMIC) at position U3 to generate different voltages required by the microcontroller and the onboard components. The Powering Scheme figure presents a graphical depiction of the powering scheme. The PMIC supports many functions like on-chip RTC and different power management functionalities like dynamic voltage control, different low power modes, and regulator supervision. It is connected to the i.MX 8M Mini via the onboard I2C bus (I2C1) (I2C Interface). The I2C address of the PMIC is 0x08.

Power Domains

phyCORE-i.MX 8M Mini Powering Scheme

External voltages:

- VDD_3V3: SOM input supply voltage

- VDD_BAT: Backup supply (connected to VBAT)

Internally generated voltages:

| VDD_SOC_VDDA_PHY_0P8 | i.MX 8M Mini SOC logic and PHY supply (VDD_SOC1-12, VDD_ARM_PLL_0P8, VDD_ANA_0P8_1-2, VDD_PCI_0P8, VDD_USB_0P8) |

| VDD_GPU_DRAM | i.MX 8M MINI 3D GPU and DRAM supply (VDD_GPU1-5, VDD_DRAM1-6, VDD_DRAM_PLL_0P8) |

| VDD_VPU | i.MX 8M MINI MIPI PLL, logic (VDD_MIPI_0P9) (0.9 V) |

| VDD_MIPI_0P9 | i.MX 8M MINI MIPI PLL, logic (VDD_MIPI_0P9) (0.9 V) |

| VDD_ARM | i.MX 8M MINI Mini ARM supply (VDD_ARM1-14) (0.8/0.9 V) |

| NVCC_DRAM_1P1V | DRAM supply (NVCC_DRAM1-13) (1.1 V) |

| VDD_1V8 | i.MX 8M MINI general 1.8 V supply (VDD_ARM_PLL_1P8, VDD_ANA0_1P8_1-2, VDD_ANA1_1P8_1-2, VDD_DRAM_PLL_1P8, VDD_USB_1P8, VDD_MIPI_1P8, VDD_PCI_1P8) (1.8 V)NVCC:SD1: i.MX 8M Mini SDIO1 supply (NVCC_SD1) (1.8/3.3 V) NVCC_SD2: i.MX 8M MINI SDIO2 supply (NVCC_SD2) (1.8/3.3 V) |

| VDDA_1V8 | i.MX 8M MINI 1.8 V analog supply (VCC_24M_XTAL_1P8. PVCC0_1P8, VCC2_1P8, NVCC_ENET, NVCC_NAND, NVCC_CLK) (1.8 V) |

| NVCC_SNVS_1P8 | i.MX 8M Mini SNVS GPIO driver supply /NVCC_SNVS_1P8) (1.8 V) |

| VCC_ENET_2V5 | i.MX 8M Mini Ethernet PHY supply (U4) (2.5 V) |

| VDD_3V3_S | i.MX 8M Mini general 3.3 V supply (NVCC_JTAG, NVCC_SAI1-3, NVCC_SAI5, NVCC_GPIO1, NVCC_I2C, NVCC_UART, NVCC_ECSPI, VCC_USB_3P3) (3.3 V) |

External Logic Supply Voltage

The voltage level of the phyCORE’s logic circuitry is VDD_3V3_S (3.3 V) which is derived from the SOM main input voltage, VDD_3V3. In order to follow the mandatory power-up and power-down sequencing for the i.MX 8M Mini, external devices have to be supplied by the I/O supply voltage VDD_3V3_S which is brought out at pin E14 of the phyCORE-Connector. The use of VDD_3V3_S ensures that external components are only supplied when the supply voltages of the i.MX 8M Mini are stable.

Warning

The current draw for VDD_3V3_S must not exceed 500 mA. Consequently, this voltage should only be used as a reference or supply voltage for level shifters. VDD_3V3_S cannot be used to supply high-powered applications. If devices with higher power consumption are connected to the phyCORE‑i.MX 8M Mini, their supply voltage should be switched on and off by use of the X_PGOOD signal. This way, the power-up and power-down sequencing will be considered even if the devices are not supplied directly by VDD_3V3_S.

Tip

If used to control or supply bus switches on the phyCORE side, VDD_3V3_S separates the supply voltages generated on the phyCORE‑i.MX 8M Mini and the supply voltages used on the carrier board/custom application. This way, voltages at the IO pins of the phyCORE-i.MX 8M Mini which are sourced from the supply voltage of peripheral devices attached to the SOM are avoided.

These voltages can cause a current flow into the controller, especially if peripheral devices attached to the interfaces of the i.MX 8M Mini are supposed to be powered while the phyCORE‑i.MX 8M Mini is in suspend mode or turned off. The bus switches can be supplied by VDD_3V3_S on the phyCORE side, or the bus switches' output enabled to the SOM can be controlled by X_PGOOD to prevent these voltages from occurring.

The use of level shifters supplied with VDD_3V3_S allows the signals to be converted according to the needs of the custom target hardware. Alternatively, signals can be connected to an open drain circuitry with a pull-up resistor attached to VDD_3V3_S.

Backup Power (VBAT)

To back up the i.MX 8M Mini's low power domain (NVCC_SNVS) and its RTC, a secondary 3.3 V voltage source can be attached to the phyCORE-i.MX 8M Mini at pin A79.

Reset

Pin C43 on the phyCORE-Connector is designated as an open-drain reset input with a pull-up resistor, that triggers a hard reset of the module. The external reset signal is connected to the enable signal of the voltage supervisor U41, which triggers a watchdog event in the PMIC resulting in a hard reset of the module. For debouncing purposes, the U41 delays the signal by 8,804 ms.

For PCB version 1518.0, 1518.3a and 1518.2 additional precautions have to be taken regarding the undervoltage detection of the phyCORE-i.MX 8M Mini. X_nPOR_IN must be held on a logical low level, as long as VDD_3V3 is below 3.135 V. If this is not considered in the design of a baseboard, there is a small chance, the SoM could enter an unspecified mode of operation. PCB version 1518.3 and higher will not require this feature any longer, yet it is good engineering practice, to monitor all voltage rails at all times.

The PMIC reset output signal POR_B is made available at the phyCORE-Connector through a buffer as the open drain signal X_nPOR_OUT_OD. X_nPOR_OUT_OD is not connected to a pull-up resistor on the module. This leaves the user the freedom to choose the voltage domain used on the target hardware.

In case of a hard reset, regardless if it was triggered internally or externally, the PMIC holds the POR_B signal low until the module voltages are at stabilized levels. The POR_B signal is released approximately 11 ms after the last module voltage is correctly generated.

In order to perform a full power cycle of the phyCORE-i.MX 8M Mini, including the SNVS domain of the PMIC and the CPU, the voltage input rail VDD_3V3 has to remain below 0,3 V for at least 600 ms.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C43 | X_nRESET_IN | VDD_3V3 | 3.3 V | I-PU | SoM reset input. Transition to low level will power cycle the SoM. Signal is pulled up to SoM input voltage rail. |

C47 | X_nPOR_IN | VDD_3V3 | 3.3 V | I-PU | Power-on reset input. May be used to prolong reset state of CPU and other attached devices. |

E19 | X_nPOR_OUT_OD | VDD_3V3 | Up to 3.3 V | OD | Power-on reset output. Requires an external pull-up resistor. Voltage range up to 3,3 V |

phyCORE-Connector Reset Pins

System Boot Configuration

i.MX 8M Mini System Boot Settings

Most features of the i.MX 8M Mini microcontroller are configured and/or programmed during the initialization routine. Essential boot features however are latched into i.MX 8M Mini registers from pre-configured pull-resistors following power-on reset (POR_B) de-assertion.

The latched in information includes:

- Boot mode selection

- Boot device selection

- Detailed boot device configuration

The internal ROM code is the first code executed during the initialization process of the i.MX 8M Mini after POR de-assertion. The ROM code detects the boot mode through pins X_BOOT_MODE0 and X_BOOT_MODE1, while the boot device is selected and configured by determining the state of the eFUSEs and/or the corresponding GPIO pins (BOOT_CFGx[14:12]).

Boot Mode Selection

The i.MX 8M Mini boot mode is determined by the logical levels of the pins X_BOOT_MODE0 and X_BOOT_MODE1 approx. 31 µs after POR_B de-assertion. X_BOOT_MODE0 and X_BOOT_MODE1 are brought out at the phyCORE‑Connector pins C15 and C16. Possible settings and the resulting boot configuration of the i.MX 8M Mini are described in the following table:

X_ BOOT_MODE1 | X_ BOOT_MODE0 | Boot Source |

|---|---|---|

0 | 0 | Fuse boot |

0 | 1 | Serial downloader |

1 | 0 | Internal boot |

1 | 1 | Reserved |

phyCORE-i.MX 8M Mini Boot Modes

The BOOT_MODE[1:0] lines have 10 kΩ pull-up and pull-down resistors populated on the module. The default boot mode on the phyCORE-i.MX 8M Mini is set to internal boot mode, hence leaving the two pins unconnected will result in the unavailability of the remaining boot mode settings. The default boot device of phyCORE-i.MX 8M Mini is eMMC at SDIO3. Once in serial downloader boot, the ROM code polls the USB1 interface, initiates the download of the code into the internal RAM, and triggers its execution from there. In serial downloader boot mode the BOOT_CFG pins are ignored. Please refer to the NXP i.MX 8M Mini Reference Manual for more detailed information.

In fuse boot and internal boot mode, the ROM code finds the bootloader in permanent memories, such as eMMC or SD-Cards, and executes it. The boot device selection and the required interface configuration are accomplished with the help of the eFUSEs and/or the corresponding GPIO input.

Boot Device Selection and Configuration

In fuse boot and internal boot mode, the ROM code uses the BOOT_CFG pin states and eFUSEs to determine the boot device and it's detailed configuration.

During development, it is advisable to set the Boot Source to “Internal boot” so that choosing and configuring the boot device using GPIO pin inputs is available. The BOOT_CFG pins are sampled shortly after POR de-assertion and, if the BT_FUSE_SEL fuse is not blown, override the values of the corresponding eFUSEs BOOT_CFGx[14:0].

The Boot Configuration Pins table lists the eFUSEs BOOT_CFGx[14:0] and the corresponding input pins. On the phyCORE‑i.MX 8M Mini, the BOOT_CFG GPIOs have 10 kΩ pull-up and pull-down resistors pre-installed to configure eFUSEs BOOT_CFGx[14:0] in accordance with the module features.

The specific boot configuration settings, set by the on-board configuration resistors, can be changed by modifying the resistors on the module or overwritten by connecting a configuration resistor (e.g. 1 kΩ) to the configuration signal. Choosing to not pull the boot configuration pins to a high or low level will lead to the configuration (other than the default configuration setting) being unavailable.

Furthermore, accidental pull resistances must be considered when designing base hardware for the phyCORE-i.MX 8M Mini. Any IC or passive component that forces a high or low level at one of the designated boot mode or boot configuration pins needs to be gated away during boot mode or boot configuration latch-in. A bus switch, buffer, or transistor circuit may yield the required results.

Please consider that any change of the default boot configuration can also influence other boot modes, which might result in faulty boot behavior. Please refer to the NXP i.MX 8M Mini Reference Manual for further information about the eFUSEs and the impact of the settings at the boot configuration pins.

The following table shows the phyCORE-i.MX 8M Mini default boot device configuration setting.

| Memory device | BOOT_CFG [14] | BOOT_CFG [13] | BOOT_CFG [12] | BOOT_CFG [11] | BOOT_CFG [10] | BOOT_CFG [9] | BOOT_CFG [8] | BOOT_CFG [7] | BOOT_CFG [6] | BOOT_CFG [5] | BOOT_CFG [4] | BOOT_CFG [3] | BOOT_CFG [2] | BOOT_CFG [1] | BOOT_CFG [0] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

eMMC U21 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

phyCORE-Connector boot configuration default setting

The following table shows an excerpt from the complete boot configuration table in the NXP i.MX 8M Mini Reference Manual, edited to represent the phyCORE-i.MX 8M Mini's available boot configuration settings.

| Memory device | BOOT_CFG [14] | BOOT_CFG [13] | BOOT_CFG [12] | BOOT_CFG [11] | BOOT_CFG [10] | BOOT_CFG [9] | BOOT_CFG [8] | BOOT_CFG [7] | BOOT_CFG [6] | BOOT_CFG [5] | BOOT_CFG [4] | BOOT_CFG [3] | BOOT_CFG [2] | BOOT_CFG [1] | BOOT_CFG [0] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SPI-NOR | 1 | 1 | 0 | 000 - eCSPI1 001 - eCSPI2 010 - eCSPI3 | SPI addressing: 0 - 3 bytes 1 - 2 bytes | Chip Select: 00 - CS#0 01 - CS#1 10 - CS#2 11 - CS#3 | Reserved | ||||||||

QSPI-NOR (FlexSPI) | 1 | 0 | 0 | 0 - FLASH auto probe disabled 1- FLASH auto probe enabled | FLASH TYPE: 000 - Device supports 3 Byte read by default 001 - Device supports 4 Byte read by default | Hold time before read from device: | SPI FLASH Auto Probe Type: 0 – QuadSPI NOR | 0 - FlexSPI FLASH dummy cycle auto-probe 0001 to 1111 - Set number of FlexSPI FLASH dummy cycles manually to chosen value | |||||||

eMMC | 0 | 1 | 0 | Port select: 00 - SDIO1 01 - SDIO2 10 - SDIO3 | Power cycle: 0 – disabled | SD loopback clock source SEL (SDR50 and SDR104 only): 0 - Through SD pad 1 - Direct | Fast boot: 0 - Regular 1 - Fast boot | Bus width: 000 - 1-Bit 001 - 4-Bit 010 - 8-Bit 101 - 4-Bit DDR (MMC 4.4) 110 - 8-Bit DDR (MMC 4.4) Remaining values are reserved | Speed: 00 - Normal 01 - High 10 - Reserved for HS200 11 - Reserved | USDHC IO voltage selection; normal mode: 0 - 3.3V 1 - 1.8V | USDHC IO voltage selection; manufacturer mode: 0 - 3.3V 1 - 1.8V | ||||

SD-Card | 0 | 0 | 1 | Port select: 00 - SDIO1 | Power cycle: 0 – disabled | SD loopback clock source SEL (SDR50 and SDR104 only): 0 - Through SD pad 1 - Direct | Fast boot: 0 - Regular 1 - Fast boot | Reserved | Bus width: 000 - 1-Bit 001 - 4-Bit | Speed: 000 - Normal/SDR12 001 - High/SDR25 010 - SDR50 011 - SDR104 101 - Reserved for DDR50 Others - Reserved | Reserved | ||||

phyCORE-i.MX 8M Mini Possible Boot Configuration Settings

The following table shows the properties of BOOT_CFG[14:0] during reset and during runtime and their location on the phyCORE-Connector, as well as their signal names.

Configuration Pin | SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|---|

BOOT_CFG[0] | A81 | X_SAI1_RXD0/ BOOT_CFG[0] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 0 during reset |

BOOT_CFG[1] | A82 | X_SAI1_RXD1/ BOOT_CFG[1] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 1 during reset |

BOOT_CFG[2] | A85 | X_SAI1_RXD2/ BOOT_CFG[2] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 2 during reset |

BOOT_CFG[3] | A86 | X_SAI1_RXD3/ BOOT_CFG[3] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 3 during reset |

BOOT_CFG[4] | A87 | X_SAI1_RXD4/ BOOT_CFG[4] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 4 during reset |

BOOT_CFG[5] | A88 | X_SAI1_RXD5/ BOOT_CFG[5] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 5 during reset |

BOOT_CFG[6] | A89 | X_SAI1_RXD6/ BOOT_CFG[6] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 6 during reset |

BOOT_CFG[7] | A90 | X_SAI1_RXD7/ BOOT_CFG[7] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 7 during reset |

BOOT_CFG[8] | A94 | X_SAI1_TXD0/ BOOT_CFG[8] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 8 during reset |

BOOT_CFG[9] | A95 | X_SAI1_TXD1/ BOOT_CFG[9] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 9 during reset |

BOOT_CFG[10] | A96 | X_SAI1_TXD2/ BOOT_CFG[10] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 10 during reset |

BOOT_CFG[11] | A97 | X_SAI1_TXD3/ BOOT_CFG[11] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 11 during reset |

BOOT_CFG[12] | A98 | X_SAI1_TXD4/ BOOT_CFG[12] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 11 during reset |

BOOT_CFG[13] | A99 | X_SAI1_TXD5/ BOOT_CFG[13] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 13 during reset |

BOOT_CFG[14] | A100 | X_SAI1_TXD6/ BOOT_CFG[14] | VDD_3V3_S | 3.3 V | I/O | Boot configuration pin 14 during reset |

phyCORE-Connector Boot Configuration Pins

i.MX 8M Nano System Boot Settings

The i.MX 8M Nano uses a boot process different from the i.MX 8M Mini. Boot devices with fixed configuration may be selected through the use of 6 Boot Mode pins, 2 of which are shared with the i.MX 8M Mini. The phyCORE-i.MX 8M Nano is pre-configured with the default Boot Mode setting eMMC boot.

| Device | BOOT_MODE5 | BOOT_MODE4 | BOOT_MODE3 | BOOT_MODE2 | BOOT_MODE1 | BOOT_MODE0 |

|---|---|---|---|---|---|---|

QSPI (FlexSPI) | 0 | 0 | 0 | 1 | 1 | 0 |

eMMC | 0 | 0 | 0 | 0 | 1 | 0 |

| SD-Card | 0 | 0 | 0 | 0 | 1 | 1 |

| Serial download | 0 | 0 | 0 | 0 | 0 | 1 |

| Fuse boot | 0 | 0 | 0 | 0 | 0 | 0 |

phyCORE-i.MX 8M Nano Possible Boot Configuration Settings

System Memory

The phyCORE‑i.MX 8M Mini provides four types of onboard memory:

One bank LPDDR4 RAM: 2 GB LPDDR4 RAM (up to 4 GB)[3]

- eMMC: 8 GB (up to 32 GB)

- Quad SPI-NOR: 32 MB (up to 256 MB)[3]

- I²C-EEPROM: 4 kB[3]

The following sections detail each memory type used on the phyCORE‑i.MX 8M Mini.

| 3. | 123 The maximum memory size listed is as of the printing of this manual. Please contact PHYTEC for more information about additional, or new module configurations available. |

LPDDR4-RAM (U2)

The RAM memory of the phyCORE‑i.MX 8M Mini is comprised of one 32 bit wide bank with two 16-bit wide LPDDR4-RAM chips in one integrated circuit. The chips are connected to the DDR interface called the DDR Controller (DDRC) of the i.MX 8M Mini microcontroller.

Typically, the LPDDR4-RAM initialization is performed by a boot loader or operating system following a power-on reset and must not be changed at a later point by any application code. When writing custom code independent of an operating system or boot loader, the RAM must be initialized by accessing the appropriate RAM configuration registers on the i.MX 8M Mini controller. Refer to the NXP i.MX 8M Mini Reference Manual for accessing and configuring these registers.

QUAD SPI-NOR (U7)

The Quad NOR flash memory at U7 is connected to the Flexible Serial Peripheral Interface A (FlexSPI A). The connected flash device uses the provided Chip Select 0 signal (QSPIA_SS0). The NOR flash device is powered by the 1.8 V supply voltage VDD_1V8. No further voltages are required to program the device.

As of the printing of this manual, these NOR flash devices generally have a life expectancy of at least 100,000 erase cycles per sector and a data retention rate of typically 20 years. Any parts that are footprint (TBGA-24 5x5) and functionally compatible may be used with the phyCORE-i.MX 8M Mini.

For more information about the NOR Flash, please refer to the NXP i.MX 8M Mini Reference Manual.

eMMC Flash Memory (U21)

The managed NAND (eMMC) flash device is powered by the supply voltages VDD_1V8 (1.8 V) and VDD_3V3_S (3.3 V). No further voltages are required for programming the device. The eMMC memory is connected to the SDIO3 interface of the i.MX 8M Mini. Any parts that are footprint (BGA153) and functionally compatible may be used with the phyCORE-i.MX 8M Mini.

For more information about the eMMC, please refer to the NXP i.MX 8M Mini Reference Manual.

I2C EEPROM (U13)

The phyCORE‑i.MX 8M Mini is populated with a 4 kB I2C[4]EEPROM at U13. This memory can be used to store configuration data or other general-purpose data. This device is accessed through I2C port 1 of the i.MX 8M Mini. The control registers for I2C port 1 are mapped between addresses 0x021A 8000 and 0x021A BFFF. Please see the NXP i.MX 8M Mini Reference Manual for detailed information on the registers.

The three lower address bits are fixed to zero which means that the EEPROM can be accessed at I2C address 0x51.

| 4. | 1 See the manufacturer’s datasheet for interfacing and operation. |

EEPROM Write Control

The Write Control (WC) signal of the EEPROM is permanently fixed to GND over resistor R106, so the EEPROM is not always write-protected.

Serial Interfaces

The phyCORE‑i.MX 8M Mini provides numerous dedicated serial interfaces, some of which are equipped with a transceiver to allow direct connection to external devices:

- Two SDIO interfaces (4 and 8-Bit)

- Four High-speed UART interfaces.

- Two High-Speed USB OTG interfaces extended directly from the i.MX 8M Mini USB 2.0 PHY

- One 10/100/1000 Mbit Ethernet interface

- Four independent I2C interfaces

- Two Serial Peripheral Interfaces (SPI), extending from the first and second SPI modules (eCSPI1 and eCSPI2) of the i.MX 8M Mini. A third interface can be implemented through the use of GPIOs. See NXP i.MX 8M Mini Reference Manual muxing options.

- Four Serial Audio Interfaces (SAI), originating from the i.MX 8M Mini I2S module.

- One PCI Express Gen. 2, extending directly from the i.MX 8M Mini PCIe PHY

- One MIPI CSI-2 interface with 4 data lanes and 1 clock lane

The following sections detail each of these serial interfaces.

SDIO Interfaces

The SDIO interfaces are part of the ultra Secured Digital Host Controller and can be used to connect external SD-Cards, eMMC, or any other device requiring an SDIO interface (examples include WiFI, I/O expansion). The phyCORE‑i.MX 8M Mini features two SDIO interfaces (4 and 8-Bit). On the phyCORE‑i.MX 8M Mini, the interface signals extend from the controller's first and second Ultra Secured Digital Host Controller (uSDHC1/uSDHC2) to the phyCORE-Connector.

uSDHC2 provides dedicated card-detect, write-protect and power enable signals. For uSDHC2 to function a pull-up resistor (eg. 10k) from X_SD2_PWR_EN to the SOM input voltage VDD_3V3 is required. This enables the uSDHC2 interface by powering the corresponding domain in the i.MX 8M Mini. This feature may be used to limit access to the CPU through an openly available SD-Card slot, or similar purposes.

uSDHC1 card-detect and write-protect functions may be implemented by using GPIOs of the i.MX 8M Mini. Refer to the NXP i.MX 8M Mini Reference Manual. For more information about SD-Cards, please refer to the manufacturer's user manual.

The tables below show the locations of the various interface signals on the phyCORE-Connector. The Ultra Secured Digital Host Controller is fully compatible with SD/SDIO 3.0 (200MHz SDR signaling for up to 100 MB/s) and MMC 5.1 (HS400 DDR for up to 400 MB/s). uSDHC1 and uSDHC3 both provide 8-Bit interfaces, and uSDHC2 provides a 4-Bit interface. Refer to the NXP i.MX 8M Mini Reference Manual for more information.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A9 | X_SD1_DATA1 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 1 input and output |

A10 | X_SD1_DATA0 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 0 input and output |

A11 | X_SD1_DATA7 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 7 input and output |

A12 | X_SD1_DATA6 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 6 input and output |

A13 | X_SD1_CLK | NVCC_SD1 | 1,8 V/ 3,3 V | O | SD1 clock output |

A14 | X_SD1_CMD | NVCC_SD1 | 1,8 V/ 3,3 V | O | SD1 command output |

A15 | X_SD1_DATA5 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 5 input and output |

A16 | X_SD1_DATA4 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 4 input and output |

A17 | X_SD1_DATA3 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 3 input and output |

A18 | X_SD1_DATA2 | NVCC_SD1 | 1,8 V/ 3,3 V | I/O | SD1 data 2 input and output |

A19 | X_SD1_RESET_B | NVCC_SD1 | 1,8 V/ 3,3 V | O | SD1 reset output |

A20 | X_SD1_STROBE | NVCC_SD1 | 1,8 V/ 3,3 V | O | SD1 strobe ouput |

SDIO1 Interface Signal Locations

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C18 | X_SD2_RESET_B | NVCC_SD2 | 1,8 V/ 3,3 V | O | SD2 reset output |

C19 | X_SD2_WP | NVCC_SD2 | 1,8 V/ 3,3 V | O | SD2 write-protect output |

C20 | X_SD2_CD_B | NVCC_SD2 | 1,8 V/ 3,3 V | O | SD2 card detect |

C21 | X_SD2_DATA1 | NVCC_SD2 | 1,8 V/ 3,3 V | I/O | SD2 data 1 input and output |

C22 | X_SD2_DATA0 | NVCC_SD2 | 1,8 V/ 3,3 V | I/O | SD2 data 0 input and output |

C23 | X_SD2_CLK | NVCC_SD2 | 1,8 V/ 3,3 V | O | SD2 clock output |

C24 | X_SD2_CMD | NVCC_SD2 | 1,8 V/ 3,3 V | O | SD2 command output |

C25 | X_SD2_DATA3 | NVCC_SD2 | 1,8 V/ 3,3 V | I/O | SD2 data 3 input and output |

C26 | X_SD2_DATA2 | NVCC_SD2 | 1,8 V/ 3,3 V | I/O | SD2 data 2 input and output |

| E20 | X_SD2_PWR_EN | VDD_3V3 | 3,3 V | I | SD2 power supply enable |

SDIO2 Interface Signal Locations

Universal Asynchronous Interface

The phyCORE‑i.MX 8M Mini provides four high-speed universal asynchronous interfaces. Hardware flow control (RTS and CTS signals) may be implemented through the use of additional GPIO signals. See muxing options in NXP i.MX 8M Mini Reference Manual for more information. Location of the signals on the phyCORE-Connector:

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C27 | X_UART1_RXD | VDD_3V3_S | 3,3 V | I/O | UART1 receive data |

C28 | X_UART1_TXD | VDD_3V3_S | 3,3 V | I/O | UART1 transmit data |

C29 | X_UART2_RXD | VDD_3V3_S | 3,3 V | I/O | UART2 receive data |

C30 | X_UART2_TXD | VDD_3V3_S | 3,3 V | I/O | UART2 transmit data |

C31 | X_UART3_RXD | VDD_3V3_S | 3,3 V | I/O | UART3 receive data |

C32 | X_UART3_TXD | VDD_3V3_S | 3,3 V | I/O | UART3 transmit data |

C33 | X_UART4_RXD | VDD_3V3_S | 3,3 V | I/O | UART4 receive data |

C34 | X_UART4_TXD | VDD_3V3_S | 3,3 V | I/O | UART4 transmit data |

UART Signal Locations

USB OTG Interfaces

The phyCORE‑i.MX 8M Mini provides two high-speed USB OTG interfaces, which use the i.MX 8M Mini’s embedded High-Speed USB 2.0 PHY.

For the use of various USB functionalities, only an external USB Standard-A (for USB host), USB Standard-B (for USB devices), or USB Mini-AB (for USB OTG) connector is needed. The applicable interface signals (DN, DP, ID, and VBUS) are located on the phyCORE‑Connector X1. The locations of the USB OTG interface signals on the phyCORE-Connector X1 can be found in the tables below.

If overcurrent and power-enable signals are needed for the USB host interface, the functionality can be easily implemented through the use of GPIOs.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A21 | X_USB1_DN | VDD_3V3_S | DIFF | I/O | Negative USB1 data signal |

A22 | X_USB1_DP | VDD_3V3_S | DIFF | I/O | Positive USB1 data signal |

A23 | X_USB1_ID | VDD_3V3_S | 3,3 V | I | USB1 OTG identification pin |

E17 | USB1_VBUS | VDD_3V3_S | 1,4 V | I | USB1 voltage bus detection |

USB1 OTG Signal Locations

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A25 | X_USB2_DN | VDD_3V3_S | DIFF | I/O | Negative USB2 data signal |

A26 | X_USB2_DP | VDD_3V3_S | DIFF | I/O | Positive USB2 data signal |

A24 | X_USB2_ID | VDD_3V3_S | 3,3 V | I | USB2 OTG identification pin |

E18 | USB2_VBUS | VDD_3V3_S | Typ. 1,4 V | I | USB2 voltage bus detection |

USB2 OTG Signal Locations

Ethernet Interface

Connection of the phyCORE‑i.MX 8M Mini to the World Wide Web or a local area network (LAN) is possible using the onboard GbE PHY at U4. It is connected to the RGMII interface of the i.MX 8M Mini. The PHY operates with a data transmission speed of 10, 100, or 1000 Mbit/s. Alternatively, the RGMII interface which is available on the phyCORE‑Connector can be used to connect an external PHY. In this case, the onboard GbE PHY (U4) must not be populated (see RGMII Interface).

Ethernet PHY (U4)

With an Ethernet PHY mounted at U4, the phyCORE‑i.MX 8M Mini has been designed for use in 10/100/1000Base-T networks. The 10/100/1000Base-T interface with its LED signals extends to the phyCORE-i.MX 8M Mini Connector X1.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C7 | X_ETH0_LED0_LINK | VCC_3V3 | Typ. 3,3 V | OD | Ethernet link LED signal |

C8 | X_ETH0_LED2_ACT | VCC_3V3 | Typ. 3,3 V | OD | Ethernet activity LED signal |

A103 | X_ETH_A_P | VCC_ENET_2V5 | DIFF | ETH_I/O | Positive Ethernet A signal |

A104 | X_ETH_A_N | VCC_ENET_2V5 | DIFF | ETH_I/O | Negative Ethernet A signal |

A1 | X_ETH_B_P | VCC_ENET_2V5 | DIFF | ETH_I/O | Positive Ethernet B signal |

A2 | X_ETH_B_N | VCC_ENET_2V5 | DIFF | ETH_I/O | Negative Ethernet B signal |

A3 | X_ETH_C_P | VCC_ENET_2V5 | DIFF | ETH_I/O | Positive Ethernet C signal |

A4 | X_ETH_C_N | VCC_ENET_2V5 | DIFF | ETH_I/O | Negative Ethernet C signal |

A5 | X_ETH_D_P | VCC_ENET_2V5 | DIFF | ETH_I/O | Positive Ethernet D signal |

A6 | X_ETH_D_N | VCC_ENET_2V5 | DIFF | ETH_I/O | Negative Ethernet D signal |

Ethernet Signal Locations

The onboard GbE PHY supports HP Auto-MDIX technology, eliminating the need for a direct-connect LAN or a cross-over patch cable. It detects the TX and RX pins of the connected device and automatically configures the PHY TX and RX pins accordingly. The Ethernet PHY also features an auto-negotiation to automatically determine the best speed and duplex mode.

The Ethernet PHY is connected to the RGMII interface of the i.MX 8M Mini. Please refer to the NXP i.MX 8M Mini Reference Manual for more information about this interface.

In order to connect the module to an existing 10/100/1000Base-T network, some external circuitry is required. The required termination resistors on the analog signals (ETH0_A±, ETH0_B±, ETH0_C±, ETH0_D±) are integrated into the chip, so there is no need to connect external termination resistors to these signals.

Connection to external Ethernet magnetics should be done using very short signal traces. The A+/A-, B+/B-, C+/C-, and D+/D- signals should be routed as 100 Ohm differential pairs. The same applies to the signal lines after the transformer circuit. The carrier board layout should avoid any other signal lines crossing the Ethernet signals.

Ethernet PHY Reset

The Ethernet PHY at U4 can be reset with software. The reset input of the Ethernet PHY is connected to the Power-On Reset (POR) signal of the module and to the GPIO RESET_ETHPHY of the i.MX 8M Mini.

MAC Address

In a computer network such as a local area network (LAN), the MAC (Media Access Control) address is a unique computer hardware number. For a connection to the internet, a table is used to convert the assigned IP number to the hardware’s MAC address. In order to guarantee that the MAC address is unique, all addresses are managed in a central location. PHYTEC has acquired a pool of MAC addresses. The MAC address of the phyCORE‑i.MX 8M Mini is located on the bar code sticker attached to the module. This number is a 12-digit HEX value.

RGMII Interface

In order to use an external Ethernet PHY instead of the onboard GbE PHY at U8, the RGMII interface (ENET) of the i.MX 8M Mini is brought out at phyCORE-i.MX 8M Mini Connector X1.

Warning

The GbE PHY (U4) mustnot be populated on the module if the RGMII interface is used.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C1 | X_ENET_RGMII_RX_CTL | VDDA_1V8 | 1,8 V | I | RGMII receive control signal |

C2 | X_ENET_RGMII_RXC | VDDA_1V8 | 1,8 V | I | RGMII receive clock signal |

C3 | X_ENET_RGMII_RD0 | VDDA_1V8 | 1,8 V | I | RGMII receive data signal 0 |

C4 | X_ENET_RGMII_RD1 | VDDA_1V8 | 1,8 V | I | RGMII receive data signal 1 |

C5 | X_ENET_RGMII_RD2 | VDDA_1V8 | 1,8 V | I | RGMII receive data signal 2 |

C6 | X_ENET_RGMII_RD3 | VDDA_1V8 | 1,8 V | I | RGMII receive data signal 3 |

C65 | X_ENET_MDIO | VDDA_1V8 | 1,8 V | O | RGMII Management Data Input Output |

C66 | X_ENET_MDC | VDDA_1V8 | 1,8 V | O | RGMII Management Data Clock |

C67 | X_ENET_RGMII_TX_CTL | VDDA_1V8 | 1,8 V | O | RGMII transmit control signal |

C68 | X_ENET_RGMII_TXC | VDDA_1V8 | 1,8 V | O | RGMII transmit clock signal |

C69 | X_ENET_RGMII_TD0 | VDDA_1V8 | 1,8 V | O | RGMII transmit data signal 0 |

C70 | X_ENET_RGMII_TD1 | VDDA_1V8 | 1,8 V | O | RGMII transmit data signal 1 |

C71 | X_ENET_RGMII_TD2 | VDDA_1V8 | 1,8 V | O | RGMII transmit data signal 2 |

C72 | X_ENET_RGMII_TD3 | VDDA_1V8 | 1,8 V | O | RGMII transmit data signal 3 |

RGMII Interface Signal Locations

SPI Interfaces

The Serial Peripheral Interface (SPI) interface is a four-wire, bidirectional serial bus that provides a simple and efficient method for data exchange among devices. The phyCORE provides two SPI interfaces on the phyCORE‑i.MX 8M Mini Connector X1.

Each SPI interface provides one chip-select signal. The enhanced Configurable SPI (eCSPI) of the i.MX 8M Mini has three separate modules (eCSPI1, eCSPI2, and eCSPI3) which support data rates of up to 20 Mbit/s. The interface signals of the first and second modules (eCSPI1, eCSPI2) are made available on the phyCORE-Connector. The third SPI module can be made available through the i.MX 8M Mini pin muxing options. Refer to the NXP i.MX 8M Mini Reference Manual for more detailed information. All modules are master/slave configurable. The following tables list the SPI signals on the phyCORE-i.MX 8M Mini Connector X1:

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A53 | X_ECSPI1_SS0 | VDD_3V3_S | 3,3 V | O | SPI1 chip select signal |

A54 | X_ECSPI1_MOSI | VDD_3V3_S | 3,3 V | O | SPI1 master out, slave in signal |

A55 | X_ECSPI1_MISO | VDD_3V3_S | 3,3 V | I | SPI1 master in, slave out signal |

A56 | X_ECSPI1_SCLK | VDD_3V3_S | 3,3 V | O | SPI1 serial clock output signal |

SPI1 Interface Signal Locations

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A57 | X_ECSPI2_SS0 | VDD_3V3_S | 3,3 V | O | SPI2 chip select signal |

A58 | X_ECSPI2_MOSI | VDD_3V3_S | 3,3 V | O | SPI2 master out, slave in signal |

A59 | X_ECSPI2_MISO | VDD_3V3_S | 3,3 V | I | SPI2 master in, slave out signal |

A60 | X_ECSPI2_SCLK | VDD_3V3_S | 3,3 V | O | SPI2 serial clock output signal |

SPI2 Interface Signal Locations

I2C Interface

The Inter-Integrated Circuit (I2C) interface is a two-wire, bidirectional serial bus that provides a simple and efficient method for data exchange among devices. The i.MX 8M Mini contains four identical, independent Multimaster fast-mode I2C modules. The interface of three modules is available at the phyCORE-Connector. The first I2C module (I2C1) connects to the onboard EEPROM at U13 (I2C EEPROM), the PMIC at U3 (Power Management IC), the Real-Time Clock at U12, and the MIPI to LVDS converter at U5 LVDS (FlatLink). The MIPI to LVDS converter connects to the I2C1 interface through the level shifter U22. The voltage domain in this part of the bus is 1,8 V.

Tip

To ensure the proper functioning of the I2C interface, external pull resistors matching the load at the interface must be connected. There are no pull-up resistors mounted on the module. For detailed information on the voltage levels for the pull-up resistors, please refer to the i.MX 8M Mini datasheet.

The following tables list the I2C ports on the phyCORE-Connector, separated by interface:

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C39 | X_I2C2_SCL | VDD_3V3_S | 3,3 V | OD | I2C2 serial clock output signal |

C40 | X_I2C2_SDA | VDD_3V3_S | 3,3 V | OD-BI | I2C2 serial data input-output |

I2C2 Interface Signal Locations

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A61 | X_I2C3_SCL | VDD_3V3_S | 3,3 V | OD | I2C3 serial clock output signal |

A62 | X_I2C3_SDA | VDD_3V3_S | 3,3 V | OD-BI | I2C3 serial data input-output |

I2C3 Interface Signal Locations

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A63 | X_I2C4_SCL | VDD_3V3_S | 3,3 V | OD | I2C4 serial clock output signal |

A64 | X_I2C4_SDA | VDD_3V3_S | 3,3 V | OD-BI | I2C4 serial data input-output |

I2C4 Interface Signal Locations

Onboard I2C Bus

The first I2C module (I2C1) connects to the onboard EEPROM at U13 and the PMIC at U3. The following table shows the addresses of all I2C1 devices on the phyCORE-i.MX 8M Mini:

Device | Address |

|---|---|

EEPROM | 0x51 |

PMIC | 0x08 |

RTC | 0x52 |

MIPI to LVDS converter | 0x2D |

I2C1 Onboard Bus Addresses

Synchronous Audio Interface (SAI)

The phyCORE-i.MX 8M Mini features a Synchronous Audio Interface that supports full-duplex serial interfaces with frame synchronization such as I2S, AC97, and TDM. The interface is divided into four sub-interfaces: SAI1, SAI2, SAI3, and SAI5. All signals are routed directly to the phyCORE-i.MX 8M Mini Connector X1. All signals are part of the VDD_3V3_S voltage domain.

SAI1 provides 8-bit transmit and 8-bit receive functionality with receive, transmit, and master clock output. Frame synchronization is available for receive and transmit operations. The tables below show the signal locations for each SAI interface.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A81 | X_SAI1_RXD0/BOOT_CFG[0] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 0 signal |

A82 | X_SAI1_RXD1/BOOT_CFG[1] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 1 signal |

A83 | X_SAI1_RXFS | VDD_3V3_S | 3,3 V | I/O | SAI1 receive frame synchronization signal |

A84 | X_SAI1_RXC | VDD_3V3_S | 3,3 V | I/O | SAI1 receive bit clock signal |

A85 | X_SAI1_RXD2/BOOT_CFG[2] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 2 signal |

A86 | X_SAI1_RXD3/BOOT_CFG[3] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 3 signal |

A87 | X_SAI1_RXD4/BOOT_CFG[4] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 4 signal |

A88 | X_SAI1_RXD5/BOOT_CFG[5] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 5 signal |

A89 | X_SAI1_RXD6/BOOT_CFG[6] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 6 signal |

A90 | X_SAI1_RXD7/BOOT_CFG[7] | VDD_3V3_S | 3,3 V | I/O | SAI1 receive data 7 signal |

A91 | X_SAI1_MCLK | VDD_3V3_S | 3,3 V | I/O | SAI1 master clock signal |

A92 | X_SAI1_TXFS | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit frame synchronization signal |

A93 | X_SAI1_TXC | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit bit clock signal |

A94 | X_SAI1_TXD0/BOOT_CFG[8] | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 0 signal |

A95 | X_SAI1_TXD1/BOOT_CFG[9] | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 1 signal |

A96 | X_SAI1_TXD2/BOOT_CFG[10] | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 2 signal |

A97 | X_SAI1_TXD3/BOOT_CFG[11] | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 3 signal |

A98 | X_SAI1_TXD4/BOOT_CFG[12] | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 4 signal |

A99 | X_SAI1_TXD5/BOOT_CFG[13] | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 5 signal |

A100 | X_SAI1_TXD6/BOOT_CFG[14] | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 6 signal |

A101 | X_SAI1_TXD7 | VDD_3V3_S | 3,3 V | I/O | SAI1 transmit data 7 signal |

SAI1 Signal Locations

SAI2 provides 1-bit transmit and 1-bit receive functionality with receive, transmit, and master clock output. Frame synchronization is available for receive and transmit operations.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C58 | X_SAI2_TXFS/UART1_CTS_B | VDD_3V3_S | 3,3 V | I/O | SAI2 transmit frame synchronization signal |

C59 | X_SAI2_MCLK | VDD_3V3_S | 3,3 V | I/O | SAI2 master clock signal |

C60 | X_SAI2_RXD0/UART1_RTS_B | VDD_3V3_S | 3,3 V | I/O | SAI2 receive data 0 signal |

C61 | X_SAI2_TXC | VDD_3V3_S | 3,3 V | I/O | SAI2 transmit bit clock signal |

C62 | X_SAI2_TXD0 | VDD_3V3_S | 3,3 V | I/O | SAI2 transmit data 0 signal |

C63 | X_SAI2_RXC/UART1_RX | VDD_3V3_S | 3,3 V | I/O | SAI2 receive bit clock signal |

C64 | X_SAI2_RXFS/UART1_TX | VDD_3V3_S | 3,3 V | I/O | SAI2 receive frame synchronization signal |

SAI2 Signal Locations

SAI3 provides 1-bit transmit and 1-bit receive functionality with receive, transmit, and master clock output. Frame synchronization is available for receive and transmit operations.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A65 | X_SAI3_TXFS/UART2_RX | VDD_3V3_S | 3,3 V | I/O | SAI3 transmit frame synchronization signal |

A66 | X_SAI3_MCLK | VDD_3V3_S | 3,3 V | I/O | SAI3 master clock signal |

A67 | X_SAI3_TXD | VDD_3V3_S | 3,3 V | I/O | SAI3 transmit data signal |

A68 | X_SAI3_RXD/UART2_RTS_B | VDD_3V3_S | 3,3 V | I/O | SAI3 receive data signal |

A69 | X_SAI3_TXC/UART2_TX | VDD_3V3_S | 3,3 V | I/O | SAI3 transmit bit clock signal |

A70 | X_SAI3_RXC/UART2_CTS_B | VDD_3V3_S | 3,3 V | I/O | SAI3 receive bit clock signal |

A71 | X_SAI3_RXFS | VDD_3V3_S | 3,3 V | I/O | SAI3 receive frame synchronization signal |

SAI3 Signal Locations

SAI5 provides 4-bit receive functionality with receive and master clock output. Frame synchronization is available for receive operations.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

| C51 | X_SAI5_RXD3 | VDD_3V3_S | 3,3 V | I/O | SAI5 receive data 3 signal |

| C52 | X_SAI5_RXD2 | VDD_3V3_S | 3,3 V | I/O | SAI5 receive data 2signal |

| C53 | X_SAI5_RXD1 | VDD_3V3_S | 3,3 V | I/O | SAI5 receive data 1 signal |

| C54 | X_SAI5_RXD0 | VDD_3V3_S | 3,3 V | I/O | SAI5 receive data 0 signal |

C55 | X_SAI5_MCLK | VDD_3V3_S | 3,3 V | I/O | SAI5 master clock signal |

| C56 | X_SAI5_RXC | VDD_3V3_S | 3,3 V | I/O | SAI5 receive bit clock signal |

| C57 | X_SAI5_RXFS | VDD_3V3_S | 3,3 V | I/O | SAI5 receive frame synchronization signal |

SAI5 Signal Locations

PCI Express Interface

The 1-lane PCI Express interface of the phyCORE‑i.MX 8M Mini provides PCIe Gen. 2.0 functionality which supports 5 Gbit/s operations. Furthermore, the interface is fully backward compatible with the 2.5 Gbit/s Gen. 1.1 specification. Additional control signals which might be required (e.g. “present” and “wake”) can be implemented via the use of GPIOs. Please refer to the schematic of a suitable PHYTEC carrier board (e.g. phyBOARD‑Polis) for a circuit example.

Position of the PCIe signals on the phyCORE‑Connector X1:

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A27 | X_PCIe_CLK_N | VDD_1V8 | DIFF | O | PCIe negative clock signal |

A28 | X_PCIe_CLK_P | VDD_1V8 | DIFF | O | PCIe positive clock signal |

A29 | X_PCIe_TXN_N | VDD_1V8 | DIFF | O | PCIe negative transmit signal |

A30 | X_PCIe_TXN_P | VDD_1V8 | DIFF | O | PCIe positive transmit signal |

A31 | X_PCIe_RXN_N | VDD_1V8 | DIFF | I | PCIe negative receive signal |

A32 | X_PCIe_RXN_P | VDD_1V8 | DIFF | I | PCIe positive receive signal |

PCIe Interface Signal Locations

General Purpose I/Os

The following table lists all pins not used by any of the other interfaces described explicitly in this manual and which, therefore, can be used as GPIO without harming other features of the phyCORE‑i.MX 8M Mini. In addition, most pins directly routed to the phyCORE-i.MX M Mini Connector X1 can be configured as GPIO due to the multiplexing functionality of the i.MX 8M Mini.

For more details on the possible GPIO settings, see the NXP i.MX 8M Mini Reference Manual.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C36 | X_PWM1/GPIO1_IO00 | VDD_3V3_S | 3,3 V | I/O | GPIO01 00 with PWM ability |

C49 | X_GPIO1_IO08/ETH_1588_EVENT_IN | VDD_3V3_S | 3,3 V | I/O | GPIO01 08, also useable for IEEE 1588 protocol event out |

C50 | X_GPIO1_IO09/ETH_1588_EVENT_OUT | VDD_3V3_S | 3,3 V | I/O | GPIO01 09, also useable for IEEE 1588 protocol event in |

C44 | X_GPIO1_IO12 | VDD_3V3_S | 3,3 V | I/O | GPIO01 12 |

A80 | X_PWM2/GPIO1_IO13 | VDD_3V3_S | 3,3 V | I/O | GPIO01 13 with PWM ability |

C46 | X_PWM3/GPIO1_IO14 | VDD_3V3_S | 3,3 V | I/O | GPIO01 14 with PWM ability |

C45 | X_PWM4/GPIO1_IO15 | VDD_3V3_S | 3,3 V | I/O | GPIO01 15 with PWM ability |

GPIO Pin Locations

JTAG Interface

The phyCORE‑i.MX 8M Mini is equipped with a JTAG interface for downloading program code into the external flash, internal controller RAM, or for any debugging programs that are executed. Location of the JTAG pins on the phyCORE-i.MX 8M Mini Connector X1:

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

C9 | X_JTAG_TCK | VDD_3V3_S | 3,3 V | I | JTAG clock signal |

C10 | X_JTAG_TMS | VDD_3V3_S | 3,3 V | I | JTAG test mode select signal |

C11 | X_JTAG_TDO | VDD_3V3_S | 3,3 V | O | JTAG data out signal |

C12 | X_JTAG_TDI | VDD_3V3_S | 3,3 V | I | JTAG data in signal |

C13 | X_JTAG_MOD | VDD_3V3_S | 3,3 V | I | JTAG mode signal |

C14 | X_JTAG_TRST_B | VDD_3V3_S | 3,3 V | I | JTAG tap reset signal |

JTAG Interface Signal Locations

Display Interfaces

In the industrial market, LVDS is the default display with the best long-time availability. MIPI is normally used for the consumer market. For this reason, PHYTEC has added a MIPI to LVDS converter as part of the SOM design. This allows a normal LVDS display to be used in industrial applications. Alternatively, phyCORE-i.MX 8M MINI can be ordered without the converter so that a MIPI display can be used.

Warning

It is not possible to use both an LVDS and MIPI display at the same time. Only one type of display can be used at any given time.

LVDS (Flatlink)

The LVDS interface of the phyCORE-i.MX 8M Mini, using an optional MIPI to LVDS converter, is converted from the i.MX 8M Mini’s MIPI-DSI2 interface. The converter supports resolutions of up to 1920x1200 (WUXGA) at 60 frames per second with 24 bpp and reduced blanking. It is also suitable for resolutions of 1366x768 with 60 frames per second and 1280x800 at 60 frames per second, both 18 and 24 bpp. The LVDS interface is available only when U5 is mounted. Please refer to the Texas Instruments SN65DSI83 datasheet for more information.

Location of the LVDS signals on the phyCORE-i.MX 8M Mini Connector:

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A43 | X_FLATLINK_D0_N/MIPI_DSI_DATA0_N | VDD_1V8 | DIFF | O | Negative LVDS data 0 signal |

A44 | X_FLATLINK_D0_P/MIPI_DSI_DATA0_P | VDD_1V8 | DIFF | O | Positive LVDS data 0 signal |

A45 | X_FLATLINK_D1_N/MIPI_DSI_DATA1_N | VDD_1V8 | DIFF | O | Negative LVDS data 1 signal |

A46 | X_FLATLINK_D1_P/MIPI_DSI_DATA1_P | VDD_1V8 | DIFF | O | Positive LVDS data 1 signal |

A47 | X_FLATLINK_D2_N/MIPI_DSI_CLK_N | VDD_1V8 | DIFF | O | Negative LVDS data 2 signal |

A48 | X_FLATLINK_D2_P/MIPI_DSI_CLK_P | VDD_1V8 | DIFF | O | Positive LVDS data 2 signal |

A49 | X_FLATLINK_D3_N/MIPI_DSI_DATA2_N | VDD_1V8 | DIFF | O | Negative LVDS data 3 signal |

A50 | X_FLATLINK_D3_P/MIPI_DSI_DATA2_P | VDD_1V8 | DIFF | O | Positive LVDS data 3 signal |

A51 | X_FLATLINK_CLK_N/MIPI_DSI_DATA3_N | VDD_1V8 | DIFF | O | Negative LVDS clock signal |

A52 | X_FLATLINK_CLK_P/MIPI_DSI_DATA3_P | VDD_1V8 | DIFF | O | Positive LVDS clock signal |

LVDS Interface Signal Locations

MIPI-Display Serial Interface 2 (MIPI-DSI2)

The i.MX 8M Mini’s MIPI-DSI2 interface provides resolutions of up to 1920x1080 at 60 frames per second. It uses four data channels and one clock channel. The MIPI-DSI2 interface is only available if the MIPI to LVDS converter U5 is not mounted. The interface provides a maximum bit rate of 1,5 Gbit/s.

SOM Connector Pin / phyBOARD-Polis Carrier Board Connector Pin | SOM Signal Name | SOM Voltage Domain | Signal Level | Signal Type | Description |

|---|---|---|---|---|---|

A43 | X_FLATLINK_D0_N/MIPI_DSI_DATA0_N | VDD_1V8 | DIFF | O | Negative MIPI-DSI data 0 signal |

A44 | X_FLATLINK_D0_P/MIPI_DSI_DATA0_P | VDD_1V8 | DIFF | O | Positive MIPI-DSI data 0 signal |

A45 | X_FLATLINK_D1_N/MIPI_DSI_DATA1_N | VDD_1V8 | DIFF | O | Negative MIPI-DSI data 1 signal |

A46 | X_FLATLINK_D1_P/MIPI_DSI_DATA1_P | VDD_1V8 | DIFF | O | Positive MIPI-DSI data 1 signal |

A47 | X_FLATLINK_D2_N/MIPI_DSI_CLK_N | VDD_1V8 | DIFF | O | Negative MIPI-DSI clock signal |

A48 | X_FLATLINK_D2_P/MIPI_DSI_CLK_P | VDD_1V8 | DIFF | O | Positive MIPI-DSI clock signal |

A49 | X_FLATLINK_D3_N/MIPI_DSI_DATA2_N | VDD_1V8 | DIFF | O | Negative MIPI-DSI data 2 signal |

A50 | X_FLATLINK_D3_P/MIPI_DSI_DATA2_P | VDD_1V8 | DIFF | O | Positive MIPI-DSI data 2 signal |

A51 | X_FLATLINK_CLK_N/MIPI_DSI_DATA3_N | VDD_1V8 | DIFF | O | Negative MIPI-DSI data 3 signal |