# miniMODUL-537 / 509

## Hardware-Manual

Ausgabe Juli 2002

Im Buch verwendete Bezeichnungen für Erzeugnisse, die zugleich ein eingetragenes Warenzeichen darstellen, wurden nicht besonders gekennzeichnet. Das Fehlen der © Markierung ist demzufolge nicht gleichbedeutend mit der Tatsache, daß die Bezeichnung als freier Warenname gilt. Ebenso wenig kann anhand der verwendeten Bezeichnung auf eventuell vorliegende Patente oder einen Gebrauchsmusterschutz geschlossen werden.

Die Informationen in diesem Handbuch wurden sorgfältig überprüft und können als zutreffend angenommen werden. Dennoch sei ausdrücklich darauf verwiesen, daß die Firma PHYTEC Meßtechnik GmbH weder eine Garantie noch die juristische Verantwortung oder irgendeine Haftung für Folgeschäden übernimmt, die auf den Gebrauch oder den Inhalt dieses Handbuches zurückzuführen sind. Die in diesem Handbuch enthaltenen Angaben können ohne vorherige Ankündigung geändert werden. Die Firma PHYTEC Meßtechnik GmbH geht damit keinerlei Verpflichtungen ein.

Ferner sei ausdrücklich darauf verwiesen, daß PHYTEC Meßtechnik GmbH weder eine Garantie noch die juristische Verantwortung oder irgendeine Haftung für Folgeschäden übernimmt, die auf falschen Gebrauch oder falschen Einsatz der Hardbzw. Software zurückzuführen sind. Ebenso können ohne vorherige Ankündigung Layout oder Design der Hardware geändert werden. PHYTEC Meßtechnik GmbH geht damit keinerlei Verpflichtungen ein.

#### © Copyright 2002 PHYTEC Meßtechnik GmbH, D-55129 Mainz.

Alle Rechte vorbehalten. Kein Teil dieses Buches darf in irgendeiner Form ohne schriftliche Genehmigung der Firma PHYTEC Meßtechnik GmbH unter Einsatz entsprechender Systeme reproduziert, verarbeitet, vervielfältigt oder verbreitet werden.

#### Informieren Sie sich:

|                        | EUROPA                                                                           | NORD AMERIKA                                                                               |

|------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Adresse:               | PHYTEC Technologie Holding AG<br>Robert-Koch-Str. 39<br>D-55129 Mainz<br>GERMANY | PHYTEC America LLC<br>203 Parfitt Way SW, Suite G100<br>Bainbridge Island, WA 98110<br>USA |

| Angebots<br>Hotline:   | +49 (800) 0749832<br>order@phytec.de                                             | +1 (800) 278-9913<br>info@phytec.com                                                       |

| Technische<br>Hotline: | +49 (6131) 9221-31<br>support@phytec.de                                          | +1 (800) 278-9913<br>support@phytec.com                                                    |

| Fax:                   | +49 (6131) 9221-33                                                               | +1 (206) 780-9135                                                                          |

| Web Seite:             | http://www.phytec.de                                                             | http://www.phytec.com                                                                      |

#### 1. Auflage Juli 2002

| Einl | leitun | g                                               | 1   |

|------|--------|-------------------------------------------------|-----|

| 1    | Kur    | zübersicht über das miniMODUL-537/509           | 3   |

|      | 1.1    | Blockschaltbild                                 | 5   |

|      | 1.2    | Ansicht des miniMODUL-537/509                   | 6   |

| 2    | Anso   | chlußbelegung                                   | 7   |

| 3    | Jum    | per                                             | .11 |

|      | 3.1    | J1 Interner oder Externer Programmspeicher      | .12 |

|      | 3.2    | J2 Spannungsversorgung des SRAM/E²PROM U5       | .13 |

|      | 3.3    | J3 Power-Saving Modes / Watchdog-Timer          | .13 |

|      | 3.4    | J4 Oszillator-Watchdog                          | .14 |

|      | 3.5    | J5, J6 Erste Serielle Schnittstelle             | .14 |

|      | 3.6    | J7, J8 Zweite Serielle Schnittstelle            | .15 |

|      | 3.7    | J9, J10, J11 RS-485-Steuerung                   | .15 |

|      | 3.8    | J12 RS-232-Steuerung                            | .17 |

|      | 3.9    | J13 Chip-Enable der Echtzeituhr RTC72423 (U10B) |     |

|      | 3.10   | J14 Internes Programmiermodell beim C509        | .18 |

|      |        | J15 Spannungsversorgung des E²PROM/FRAM         |     |

|      | 3.12   | J16, J17 Adresse des Seriellen E²PROM/FRAM      | .19 |

|      | 3.13   | J18 Schreibschutz des E²PROM/FRAM               | .20 |

|      | 3.14   | J19 – J22 Verwendung ICE/Connect                | .20 |

| 4    |        | chermodelle                                     |     |

|      | 4.1    | Controlregister 1                               |     |

|      | 4.2    | Controlregister 2                               | .29 |

|      | 4.3    | Adreßregister                                   |     |

|      | 4.4    |                                                 |     |

| 5    | Flas   | h Speicher                                      |     |

| 6    |        | eriepufferung                                   |     |

| 7    |        | tzeituhr RTC-8564 (U12)                         |     |

| 8    |        | elles EEPROM/FRAM (U13)                         |     |

| 9    |        | nnische Daten                                   |     |

| 10   |        | weise zum Umgang mit dem Modul                  |     |

| Inda |        |                                                 | 45  |

### **Bild- und Tabellenverzeichnis**

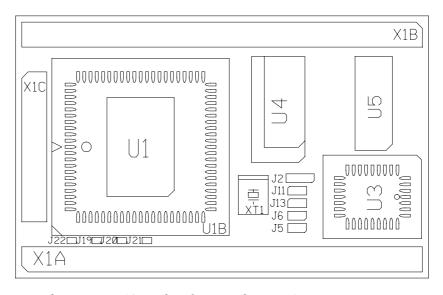

| Bild 1:    | Blockschaltbild5                                                 |

|------------|------------------------------------------------------------------|

| Bild 2:    | Ansicht des miniMODUL-537/509 (Controllerseite)6                 |

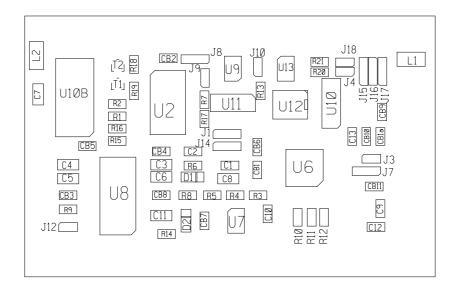

| Bild 3:    | Ansicht des miniMODUL-537/509 (Platinenunterseite)6              |

| Bild 4:    | Lage der Pins                                                    |

| Bild 5:    | Zählweise der Jumper11                                           |

| Bild 6:    | Lage der Jumper (Ansicht Platinenoberseite)11                    |

| Bild 7:    | Lage der Jumper (Ansicht Platinenunterseite)                     |

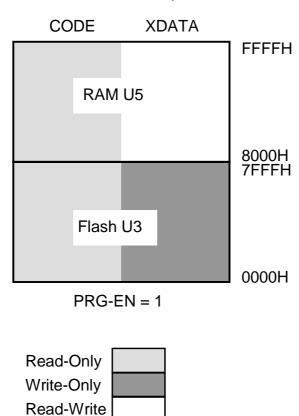

| Bild 8:    | Default-Speichermodell nach Hardware-Reset                       |

| Bild 9:    | Flash-Programmiermodell des miniMODUL-537/509 24                 |

| Bild 10:   | Aufteilung des I/O-Bereichs                                      |

| Bild 11:   | Beispiel-Speichermodell                                          |

| Bild 12:   | Speicherbereiche des Flash                                       |

| Bild 13:   | Mechanische Abmaße41                                             |

|            |                                                                  |

| Tabelle 1: | Pinout mit Erläuterung                                           |

| Tabelle 2: | J1 Auswahl Interner oder Externer Programmspeicher 12            |

| Tabelle 3: | J2 Konfiguration Spannungsversorgung SRAM/E <sup>2</sup> PROM 13 |

| Tabelle 4: | J3 Konfiguration Power-Saving Modes / Watchdog-Timer 13          |

| Tabelle 5: | J4 Konfiguration Oszillator-Watchdog                             |

| Tabelle 6: | J5, J6 Konfiguration Erste Serielle Schnittstelle14              |

| Tabelle 7: | J7, J8 Konfiguration Zweite Serielle Schnittstelle               |

| Tabelle 8: | J9 Konfiguration RS-485 Sendesteuerung                           |

| Tabelle 9: | J10 Konfiguration RS-485 Empfangssteuerung                       |

| Tabelle 10 | : J11 Konfiguration RS-485 Datenausgang                          |

| Tabelle 11 | : J12 Konfiguration RS-232 Steuerung                             |

| Tabelle 12 | : J13 Konfiguration Chip-Enable RTC72423                         |

| Tabelle 13 | : J14 Konfiguration Programmier-Modus C509                       |

| Tabelle 14: J15 Konfiguration Spannungsversorgung des E <sup>2</sup> PROM/FRAM | 19  |

|--------------------------------------------------------------------------------|-----|

| Tabelle 15: J16, J17 Konfiguration Adresse Serielles E <sup>2</sup> PROM/FRAM  | 19  |

| Tabelle 16: J18 Konfiguration E <sup>2</sup> PROM/FRAM Schreibschutz           | 20  |

| Tabelle 17: Controlregister 1                                                  | 23  |

| Tabelle 18: Controlregister 2                                                  | 29  |

| Tabelle 19: Adreßregister                                                      | 30  |

| Tabelle 20: Maskenregister                                                     | 31  |

| Tabelle 21: Beispiel zur Verwendung von Adreß- und Maskenregiste               | r32 |

| Tabelle 22: Bestückungsoptionen für U13                                        | 39  |

| Tabelle 23: E <sup>2</sup> PROM/FRAM Schreibschutz                             | 39  |

| Tabelle 24: E <sup>2</sup> PROM/FRAM Adresse                                   | 40  |

## **Einleitung**

Dieses Handbuch beschreibt nur die Schaltung und Funktionen des miniModul-537 / 509, nicht aber den Controller SAB80C537 selbst. Es wird ergänzt durch das entsprechende Controllerhandbuch z.B. "SAB80C537 User's Manual " sowie die Dokumentation zu gegebenenfalls mitgelieferter Software. Bitte beachten Sie daher auch diese Dokumentationen.

In diesem Handbuch sowie im dazugehörigen Schaltplan werden low-aktive Signale durch einen Schrägstich "/" vor dem Signalnamen gekennzeichnet (z.B. "/RD"). Die Darstellung "0" deutet auf eine logische Null oder low-Pegel hin, während "1" für eine logische Eins oder high-Pegel steht.

## Anmerkungen zum EMV-Gesetz für das miniModul-537 / 509

Das miniModul-537 / 509 (im Folgenden Produkt genannt) ist als Zulieferteil für den Einbau in ein Gerät (Weiterverarbeitung durch Industrie (siehe § 5 Abs. 5 EMVG)) bzw. als Evaluierungsboard für den Laborbetrieb (zur Hardware- und Softwareentwicklung) bestimmt.

### Achtung!

Das Produkt ist ESD empfindlich und darf nur an ESD geschützten Arbeitsplätzen von geschultem Fachpersonal ausgepackt und gehandhabt bzw. verarbeitet werden. Im Betrieb dürfen ohne weitere Schutzbeschaltung und Prüfung keine Leitungen von mehr als 3 m Länge an die Verbinder angeschlossen werden.

Das Produkt erfüllt die Anforderungen des EMVG (CE-Konformität) nur für den in diesem Handbuch beschriebenen Anwendungsbereich unter Einhaltung der gegebenen Hinweise zur Inbetriebnahme.

Nach dem Einbau in ein Gerät oder bei Änderungen/Erweiterungen an diesem Produkt muß die Konformität nach dem EMV-Gesetz neu festgestellt und bescheinigt werden. Erst danach dürfen solche Geräte in Verkehr gebracht werden.

#### Auszug aus dem EMVG § 5 Abs. 5

Geräte, die ausschließlich zur Verwendung in eigenen Laboratorien, Werkstätten und Räumen hergestellt, Anlagen, die erst am Betriebsort zusammengesetzt werden, und Netze bedürfen keiner EG-Konformitätserklärung und CE-Kennzeichnung.

Dies gilt auch für Bausätze, die ausschließlich für Funkamateure im Sinne des § 1 Abs. 2 hergestellt und bestimmt sind.

Geräte, die ausschließlich als Zulieferteile oder Ersatzteile zur Weiterverarbeitung durch Industrie, Handwerk oder sonstige auf dem Gebiet der elektromagnetischen Verträglichkeit fachkundige Betriebe hergestellt und bereitgehalten werden, brauchen weder die Schutzanforderungen gemäß § 4 Abs. 1 einzuhalten noch bedürfen sie einer EG-Konformitätserklärung oder CE-Kennzeichnung, vorausgesetzt, es handelt sich dabei nicht um selbständig betreibbare Geräte.

Das miniModul-537 / 509ist ein Modul aus der Serie der nano-/micro-/miniModule der Firma PHYTEC, die eine Bestückung mit verschiedenen Controllern erlauben, und dadurch eine Vielzahl von Funktionen und Konfigurationen ermöglichen.

PHYTEC unterstützt alle gängigen 8- und 16-bit-Controller auf zwei Arten:

- als Grundlage für Starter Kits, die die Kombination mit benutzereigenen Schaltungen auf einem eigens dafür vorgesehenen Wrap-Feld erlauben und

- als universelle, sofort einsetzbare, voll funktionsfähige micro- und miniMODULe, die direkt in die benutzereigene Peripherie-Schaltung eingesteckt werden können.

Mit dem Konzept der Microcontroller-Module von PHYTEC ist es Entwicklungsingenieuren möglich, Entwicklungszeiten zu verkürzen, Entwicklungskosten zu reduzieren und die Durchführung eines Projektes von der Idee bis zur Markteinführung wesentlich zu beschleunigen. Für weitere Informationen wenden Sie sich bitte an folgende Adressen:

|            | EUROPA                                                                           | NORD AMERIKA                                                                               |

|------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Adresse:   | PHYTEC Technologie Holding AG<br>Robert-Koch-Str. 39<br>D-55129 Mainz<br>GERMANY | PHYTEC America LLC<br>203 Parfitt Way SW, Suite G100<br>Bainbridge Island, WA 98110<br>USA |

| Web Seite: | http://www.phytec.de                                                             | http://www.phytec.com                                                                      |

| e-mail:    | info@phytec.de                                                                   | info@phytec.com                                                                            |

| Tel.:      | +49 (6131) 9221-0                                                                | +1 (800) 278-9913                                                                          |

| Fax:       | +49 (6131) 9221-33                                                               | +1 (206) 780-9135                                                                          |

#### 1 Kurzübersicht über das miniMODUL-537/509

Das miniMODUL-537/509 ist ein universelles Microcontrollerboard im Scheckkartenformat. Es kann mit den Microcontrollern 80C537 oder alternativ mit dem C509 von Infineon bestückt werden. Der C509 Controller kann mit maximal 16 MHz getaktet werden und erreicht damit die Rechenleistung eines mit 32 MHz getakteten 8032 (375 ns Zykluszeit).

Die controllerspezifischen Eigenschaften entnehmen Sie bitte dem Handbuch zum jeweiligen Microcontroller, im Hardware-Manual zum miniMODUL-537/509 wird auf keinerlei Besonderheiten des jeweiligen Microcontrollers näher eingegangen, da diese für die grundlegende Funktion des miniMODUL-537/509 ohne Belang sind.

Das vorliegende Handbuch beschreibt das miniMODUL-537/509 in der Platinenversion PCB-No. 1108.2.

## Das miniMODUL-537/509 bietet folgende Features:

- Rechner im Scheckkartenformat 55 x 85 mm durch Einsatz moderner SMD-Technik

- verbesserte Störsicherheit durch Multilayer-Technik

- aufsetzbar auf die Anwendungsschaltung wie ein großer Chip

- Infineon Controller 80C537 (auch 80C517...517A) im PLCC84 Gehäuse oder C509 im QFP100 Gehäuse, befehlskompatibel zur Familie der 8051-Prozessoren von INTEL

- einzige Versorgungsspannung 5 VDC, typ. <110 mA

- bis zu 512 kByte Flash on-board (PLCC)

- on-board Flash-Programmierung

- keine separate Programmierspannung durch Verwendung von 5 V-Flash-Bausteinen

- bis zu 160 kByte RAM on-board (SMD)

- wahlweise auch mit 32 kByte EEPROM (SMD)

- alle Ports sowie Daten- und Adreßleitungen am Platinenrand über Stiftleisten verfügbar

- flexible, per Software konfigurierbare Adreßdecodierung durch komplexen Logikbaustein

- Banklatches für Flash und RAM im Adreßdekoder integriert

- wahlweise Schnittstellentreiber für zwei RS-232 oder eine RS-232- und eine RS-485-Schnittstelle

- wahlweise zwei Echtzeituhren RTC8583 oder RTC72423

- Echtzeituhren und RAMs mit externer Batterie pufferbar

- freie Chip-Select Signale für einfachen Anschluß externer Peripherie

#### Zusätzliche Features, ab Platinennummer 1108.2

- Wahlweise mit einer der Echtzeituhren RTC8583, RTC8564 oder RTC72423 bestückbar

- bis zu 32 kByte EEPROM bzw. 8 kByte FRAM

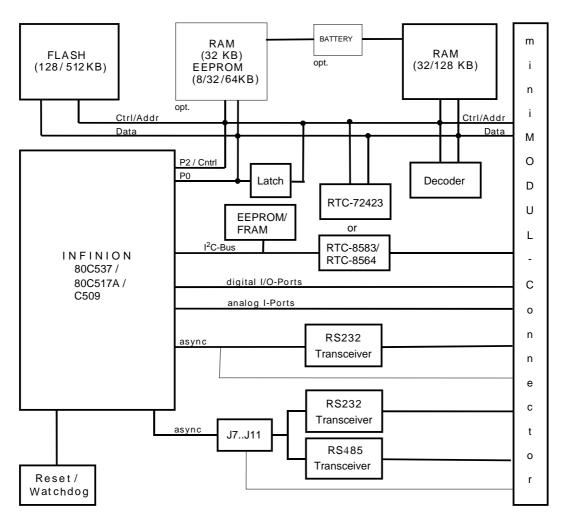

### 1.1 Blockschaltbild

Bild 1: Blockschaltbild

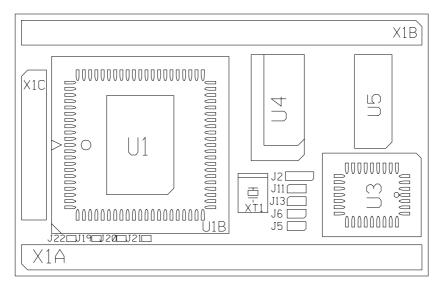

### 1.2 Ansicht des miniMODUL-537/509

Bild 2: Ansicht des miniMODUL-537/509 (Controllerseite)

*Bild 3:* Ansicht des miniMODUL-537/509 (Platinenunterseite)

## 2 Anschlußbelegung

Es sei ausdrücklich darauf hingewiesen, daß bei allen Modulanschlüssen unbedingt die Maximalspannungen und -ströme nicht überschritten werden dürfen. Die Grenzwerte hierfür können Sie dem jeweiligen Controller-Handbuch entnehmen. Da eventuell auftretende Störungen stark vom Einsatzgebiet bzw. Anwendungsfall abhängen, obliegt es der Verantwortung des Anwenders, in entsprechend kritischer Umgebung, geeignete Schutzmaßnahmen zu treffen.

Wie in *Bild 4* dargestellt, werden alle relevanten Signale an drei Seiten des Moduls an den Platinenrand geführt, dort ist eine Bestückung mit Stiftleisten im Rastermaß 2,54 mm möglich. Die folgende *Tabelle 1* gibt Ihnen eine Übersicht über die Belegung aller Anschlüsse.

Bild 4: Lage der Pins

| Pin Nr.   | Bezeichnung | Beschreibung                                                    |  |

|-----------|-------------|-----------------------------------------------------------------|--|

| 1, 2      | NC          | nicht verwendet                                                 |  |

| 310       | P4.0P4.7    | Port 4                                                          |  |

| 11        | MDIS        | Memory-Disable-Eingang für U4 und U5                            |  |

| 12        | /PSEP       | trennbares /Program-Store-Enable-Signal des                     |  |

|           |             | Controllers <sup>1</sup>                                        |  |

| 13        | /WRP        | trennbares /WR-Signal des Controllers <sup>1</sup>              |  |

| 14        | /RDP        | trennbares /RD-Signal des Controllers <sup>1</sup>              |  |

| 1520      | P3.0P3.5    | Port 3                                                          |  |

| 21        | /WR , P3.6  | trennbares /WR-Signal des Moduls <sup>1</sup>                   |  |

| 22        | /RD, P3.7   | trennbares /RD-Signal des Moduls <sup>1</sup>                   |  |

| 2330      | P1.7P1.0    | Port 1                                                          |  |

| 31        | /PSEN       | trennbares /Program-Store-Enable-Signal des Moduls <sup>1</sup> |  |

| 32        | VPD         | Spannungsausgang für externe Pufferung                          |  |

| 33        | RES         | Reset-Ausgang des Moduls                                        |  |

| 34        | /RES        | trennbarer /Reset-Ein-/Ausgang des Moduls <sup>1</sup>          |  |

|           |             | (Open-Kollektor)                                                |  |

| 35        | /CS1        | vordekodiertes Chip-Select Signal #1                            |  |

| 36        | /CS2        | vordekodiertes Chip-Select Signal #2                            |  |

| 37        | /CS3        | vordekodiertes Chip-Select Signal #3                            |  |

| 38        | /PFO        | /Power-Fail-Ausgang                                             |  |

| 39        | PFI         | Power-Fail-Eingang                                              |  |

| 40        | /HPD        | opt. /HWPD-Eingang bei 80C517A und C509                         |  |

| 41,43,51, | TI1TI4      | Transmitter Eingänge 1-4 des RS-232-                            |  |

| 52        |             | Treibers (TI1 und TI2 über J5 bzw. J8 mit                       |  |

|           |             | seriellen Schnittstellen des Controllers                        |  |

|           |             | verbunden)                                                      |  |

| 42        | VBAT        | Eingang für Anschluß externe Pufferbatterie                     |  |

| 44,54,50  | RO1RO3      | Receiver Ausgänge 1-3 des RS-232-Treibers                       |  |

|           |             | (RO1 und RO2 über J6 bzw. J7 mit seriellen                      |  |

|           |             | Schnittstellen des Controllers verbunden)                       |  |

| 45,55,49  | RI1RI3      | Receiver Eingänge 1-3 des RS-232-Treibers                       |  |

| 47,46,48, | TO1TO4      | Transmitter Ausgänge 1-4 des RS-232-                            |  |

| 56        |             | Treibers                                                        |  |

| 53        | RSDIS       | RS-232-Treiber-Disable Eingang                                  |  |

| 57        | ALE         | Adresslatch-Enable-Ausgang                                      |  |

| 58        | /RESP       | trennbares Reset-Signal des Controllers <sup>1</sup>            |  |

Für die Verwendung von Emulatoren können die Controllersignale /XXP von den im restlichen Modul verwendeten Signalen /XX getrennt und demzufolge von außen eingespeist werden. Hiervon betroffen sind die Signale /PSEN, /RD, /WR und /RES.

| Pin-Nr. | Bezeichnung  | Beschreibung                                                        |  |

|---------|--------------|---------------------------------------------------------------------|--|

| 59      | /CSRTC       | Chip-Select Signal der RTC72423 (über Jumper                        |  |

|         |              | J13 mit /CS1 verbunden)                                             |  |

| 60      | /IRTC        | Interupt-Ausgang der beiden RTC's                                   |  |

| 61      | /RESI        | /Reset-Eingang des Moduls                                           |  |

| 62      | WDP          | Watchdog Eingang des Moduls                                         |  |

| 63,64   | NC           | nicht verwendet                                                     |  |

| 65,66   | VCC          | Versorgungsspannung +5 V =                                          |  |

| 6774    | AD7AD0       | Datenbus (Port 0), gemultiplext mit Adreßbus                        |  |

|         |              | (Low-Byte)                                                          |  |

| 7582    | A7A0         | Adreßbus (Low-Byte)                                                 |  |

| 8390    | A9,A8,A11,   | Adreßbus (High-Byte)                                                |  |

|         | A10,A13,A12, |                                                                     |  |

|         | A15,A14      |                                                                     |  |

| 91      | PRGEN        | Prog-Enable-Eingang                                                 |  |

|         |              | (nur C509 Controller )                                              |  |

| 92      | NC           | nicht verwendet                                                     |  |

| 93      | DE           | Daten-Enable-Eingang des RS-485-Treibers (mit                       |  |

|         |              | Pin 13 von U11 beschaltet)                                          |  |

| 94      | D            | Daten-Eingang des RS-485-Transmitters (über                         |  |

|         |              | Jumper J8 mit serieller Schnittstelle des                           |  |

|         |              | Controllers verbunden)                                              |  |

| 95      | В            | differentielle B-Leitung des RS-485-Treibers                        |  |

| 96      | R            | Daten-Ausgang des RS-485-Receivers (über                            |  |

|         |              | Jumper J7 mit serieller Schnittstelle des                           |  |

|         |              | Controllers verbunden)                                              |  |

| 97      | A            | differentielle A-Leitung des RS-485-Treibers                        |  |

| 98      | /R           | invertierter Daten-Ausgang des RS-485-                              |  |

|         |              | Receivers (über Jumper J11 mit P3.2 des                             |  |

| 00      | /DE          | Controllers verbunden)                                              |  |

| 99      | /DE          | invertierender Data-Enable-Eingang des                              |  |

|         |              | RS-485-Transmitters (über J9 mit P5.1 des                           |  |

| 100     | /DE          | Controllers verbunden) /Receive-Enable-Eingang des RS-485-Receivers |  |

| 100     | /RE          | (über Jumper J10 mit GND verbunden)                                 |  |

| 101108  | P9.7P9.0     | Port 9 (nur C509 Controller)                                        |  |

| 101108  | P5.7P5.0     | Port 5                                                              |  |

| 117     | /RO          | /Reset-Ausgang des Controllers                                      |  |

| 117     | /RO<br>/PE   | Watchdog-Timer / Power-Saving-Modes des                             |  |

| 110     | /112         | Controllers (über Jumper J3 mit GND                                 |  |

|         |              | verbunden)                                                          |  |

| 119126  | P6.0P6.7     | Port 6                                                              |  |

| 127,128 | GND          | Schaltungsmasse 0 V                                                 |  |

|         | ,            |                                                                     |  |

| Pin-Nr.  | Bezeichnung | Beschreibung                           |

|----------|-------------|----------------------------------------|

| 129,133, | AGND        | Bezugsmasse Analogeingänge 0 V         |

| 137,141, |             |                                        |

| 143,145, |             |                                        |

| 147,149  |             |                                        |

| 131,135, | AN12AN14    | Analogeingänge AN12AN14                |

| 139      |             | (nur C509 Controller)                  |

| 136,134, | AN11AN0     | Analogeingänge AN11AN0                 |

| 132,130, |             |                                        |

| 152,150, |             |                                        |

| 148,146, |             |                                        |

| 144,142, |             |                                        |

| 140,138  |             |                                        |

| 151      | AREF        | Referenzspannung Analogeingänge +5 V = |

Tabelle 1: Pinout mit Erläuterung

Signale, die in diesem Handbuch mit einem führenden Schrägstrich gekennzeichnet sind (wie z.B. /RES) sind aktiv-low Signale.

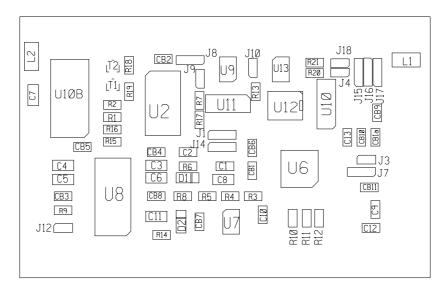

## 3 Jumper

Das miniMODUL-537/509 besitzt zur Konfiguration 22 Lötjumper, die teilweise bereits bei der Auslieferung vorverbunden sind. Das *Bild 5* verdeutlicht die verwendete Zählweise bei den Jumpern, *Bild 6* und *Bild 7* die Lage der Jumper auf der jeweiligen Platinenseite.

Bild 5: Zählweise der Jumper

Bild 6: Lage der Jumper (Ansicht Platinenoberseite)

Bild 7: Lage der Jumper (Ansicht Platinenunterseite)

## 3.1 J1 Interner oder Externer Programmspeicher

Jumper J1 dient zur Selektion des controller-internen ROM/Flash bei entsprechenden Controller-Typen. Dieser Jumper ist immer in Position 1+2 geschlossen, da PHYTEC standardmäßig nur ROM-lose Controller ausliefert. Dadurch wird nach einem Hardware-Reset das im externen Programmspeicher abgelegte Programm abgearbeitet.

| Code-Zugriff              | J1        |

|---------------------------|-----------|

| externer Programmspeicher | $1 + 2^*$ |

| interner Programmspeicher | 2 + 3     |

<sup>\* =</sup> Default-Einstellung

Tabelle 2: J1 Auswahl Interner oder Externer Programmspeicher

#### 3.2 J2 Spannungsversorgung des SRAM/E<sup>2</sup>PROM U5

Mit dem Jumper J2 kann die Versorgungsquelle für den Speicherbaustein U5 in Abhängigkeit des Bausteintyps ausgewählt werden. Bei bestücktem EEPROM auf U5 ist die Versorgung mit VCC zwingend erforderlich (J2 = 1+2), um ein vorzeitige Entladung einer eventuell angeschlossenen Pufferbatterie zu vermeiden. Ein RAM hingegen sollte über VPD (J2 = 2+3) versorgt werden, damit im Falle einer Batteriepufferung der Dateninhalt auch bei abgeschaltetem VCC gewährleistet ist.

Es ergeben sich folgende Konfigurationen:

| Spannungsversorgung SRAM/E <sup>2</sup> PROM (U5)        | J2        |

|----------------------------------------------------------|-----------|

| VCC als Versorgungsspannung des SRAM/E <sup>2</sup> PROM | $1 + 2^*$ |

| VPD als Versorgungsspannung des SRAM/E <sup>2</sup> PROM | 2 + 3     |

<sup>\* =</sup> Default-Einstellung

Tabelle 3: J2 Konfiguration Spannungsversorgung SRAM/E<sup>2</sup>PROM

## 3.3 J3 Power-Saving Modes / Watchdog-Timer

Durch Öffnen des Jumpers J3 kann die Aktivierung der Power-Saving Modes des Controllers gesperrt werden, gleichzeitig wird der Watchdog-Timer automatisch nach Reset gestartet. Im Auslieferungzustand ist der Watchdog-Timer zunächst inaktiv. Sie können diesen aber per Software aktivieren oder die Power-Saving Modes des Controllers benutzen.

| <b>Power-Saving Modes</b> | Watchdog-Timer | J3           |

|---------------------------|----------------|--------------|

| freigegeben               | gesperrt       | geschlossen* |

| gesperrt                  | freigegeben    | offen        |

<sup>\* =</sup> Default-Einstellung

Tabelle 4: J3 Konfiguration Power-Saving Modes / Watchdog-Timer

#### 3.4 J4 Oszillator-Watchdog

Der Oszillator-Watchdog ist im Auslieferungzustand aktiviert und ermöglicht so einen schnellen Power-On-Reset und einen sicheren Betrieb des Controllers.

Es ergeben sich folgende Konfigurationen:

| Oszillator-Watchdog | J4          |

|---------------------|-------------|

| aktiv               | offen*      |

| inaktiv             | geschlossen |

<sup>\* =</sup> Default-Einstellung

Tabelle 5: J4 Konfiguration Oszillator-Watchdog

#### 3.5 J5, J6 Erste Serielle Schnittstelle

Über die Jumper J5 und J6 lassen sich die Signale der ersten seriellen Schnittstelle (Serial0) des Controllers mit dem RS-232-Transceiver verbinden. Zudem sind die Controllerpins immer mit TTL-Pegel direkt an den Modulpins 15 und 16 (i.e. P3.0 und P3.1) verfügbar. Im Auslieferungszustand ist die erste serielle Schnittstelle des Controllers mit dem RS-232-Transceiver verbunden, die entsprechenden RS-232-Signale liegen an den Modulpins 45 und 47 an.

| Signalpegel Erste Serielle<br>Schnittstelle | J5           | <b>J</b> 6   |

|---------------------------------------------|--------------|--------------|

| RS-232 (Modulpins 45 und 47)                | geschlossen* | geschlossen* |

| TTL (Modulpins 15 und 16)                   | offen        | offen        |

<sup>\* =</sup> Default-Einstellung

Tabelle 6: J5, J6 Konfiguration Erste Serielle Schnittstelle

#### 3.6 J7, J8 Zweite Serielle Schnittstelle

Über die Jumper J7 und J8 lassen sich die Signale der zweiten seriellen Schnittstelle (Serial1) des Controllers wahlweise mit dem RS-232- oder dem RS-485-Transceiver verbinden. Auch diese Controllerpins sind zudem immer mit TTL-Pegel direkt an den Modulpins 120 und 121 (i.e. P6.1 und P6.2) verfügbar.

Es ergeben sich folgende Konfigurationen:

| Signalpegel Zweite Serielle Schnittstelle | J7     | <b>J8</b> |

|-------------------------------------------|--------|-----------|

| RS-232 (Modulpins 46 und 55)              | 2 + 3* | 2 + 3*    |

| TTL (Modulpins 120 und 121)               | offen  | offen     |

| RS-485 (Modulpins 95 und 97)              | 1 + 2  | 1 + 2     |

<sup>\* =</sup> Default-Einstellung

Tabelle 7: J7, J8 Konfiguration Zweite Serielle Schnittstelle

### 3.7 J9, J10, J11 RS-485-Steuerung

Durch Schließen des Jumpers J9 wird der invertierende Data-Enable Eingang des RS-485-Transceivers mit dem Pin P5.1 des Controllers verbunden. Auf diese Weise kann eine softwaregesteuerte Freigabe des RS-485-Transmitters erfolgen.

| RS-485-Transmitter | <b>J</b> 9  | P5.1       | RES        |

|--------------------|-------------|------------|------------|

| Sendesperre        | offen*      | don't care | don't care |

|                    | geschlossen | don't care | high       |

| Sendefreigabe      | geschlossen | low        | low        |

|                    | geschlossen | high       | don't care |

<sup>\*=</sup> Default-Einstellung

Tabelle 8: J9 Konfiguration RS-485 Sendesteuerung

Durch Schließen des Jumpers J10 wird die Empfangsbereitschaft des RS-485-Transceivers hergestellt.

Es ergeben sich folgende Konfigurationen:

| RS-485-Receiver  | J10         |

|------------------|-------------|

| Empfangssperre   | offen*      |

| Empfangsfreigabe | geschlossen |

<sup>\*=</sup> Default-Einstellung

Tabelle 9: J10 Konfiguration RS-485 Empfangssteuerung

Durch Schließen des Jumpers J11 wird der invertierte Daten-Ausgang des RS-485-Empfängers mit dem Pin P3.2 des Controllers verbunden. Da dieser Pin bitadressierbar ist, kann auf diese Weise mittels bitadressierenden Befehlen auf den Zustand des Daten-Ausgangs reagiert werden.

| P3.2 des Controllers       | J11         |

|----------------------------|-------------|

| nicht verbunden            | offen*      |

| verbunden mit invertiertem | geschlossen |

| Daten-Ausgang              |             |

<sup>\*=</sup> Default-Einstellung

Tabelle 10: J11 Konfiguration RS-485 Datenausgang

#### 3.8 J12 RS-232-Steuerung

Durch Öffnen des Jumpers J12 kann der RS-232-Transceiver deaktiviert werden. In diesem Falle ist eine Steuerung der Aktivität des Transceivers über den Eingang RSDIS des Moduls (Modulpin 53) möglich. Im Auslieferungszustand ist der Jumper J12 geschlossen und somit der RS-232-Transceiver aktiviert.

Es ergeben sich folgende Konfigurationen:

| RS-232-Transceiver | J12          | RSDIS        |

|--------------------|--------------|--------------|

| aktiviert          | geschlossen* | unbeschaltet |

|                    | offen        | low          |

| deaktiviert        | offen        | unbeschaltet |

|                    | offen        | high         |

<sup>\*=</sup> Default-Einstellung

Tabelle 11: J12 Konfiguration RS-232 Steuerung

### 3.9 J13 Chip-Enable der Echtzeituhr RTC72423 (U10B)

Bei geschlossenem Jumper J13 wird die RTC72423 mit dem vordekodierten Chip-Select Signal /CS1 des Adressdecoders verbunden. Bei geöffnetem Jumper J13 kann über das Signal /CSRTC des Moduls (Modulpin 59) ein beliebiges Chip-Select Signal angeschlossen werden.

Aus Gründen der Kompatibilität zu älteren Modulen ist dieser Jumper im Auslieferungszustand offen.

| Chip-Enable RTC-72423 (U10B)   | J13         |

|--------------------------------|-------------|

| externes /CSRTC an Modulpin 59 | offen*      |

| /CS1 vom Adressdecoder         | geschlossen |

<sup>\*=</sup> Default-Einstellung

Tabelle 12: J13 Konfiguration Chip-Enable RTC72423

#### 3.10 J14 Internes Programmiermodell beim C509

Der Jumper J14 ist nur relevant bei Verwendung eines C509 Controllers. Bei Verbindung zwischen den Pads 2+3 wird ein optionales Programmiermodell des C509 freigegeben, welches per Software aktiviert werden kann. Hierbei werden die XDATA- und CODE-Bereiche ausgetauscht, so daß man aus einer im RAM ablaufenden Applikation ein Flash Speicher programmieren kann. Hierzu existiert ein spezielles /WRF-Signal als Schreibsignal für das Flash. Da PHYTEC diesen Modus allerdings Programmierung der on-board Flash-Speichers verwendet, ist das Board auch nicht für dessen Einsatz vorgesehen, so daß der Jumper 14 auf 1+2 geschlossen werden sollte.

Es ergeben sich folgende Konfigurationen:

| Programmier-Modus C509 | J14    |

|------------------------|--------|

| gesperrt               | 1 + 2* |

| freigegeben            | 2 + 3  |

<sup>\*=</sup> Default-Einstellung

Tabelle 13: J14 Konfiguration Programmier-Modus C509

## 3.11 J15 Spannungsversorgung des E<sup>2</sup>PROM/FRAM

Zur Pufferung der Daten in einem FRAM-Speicher muss dieser an VPD angeschlossen werden. Bei Ausfall der Hauptversorgungsspannung VCC schaltet der RESET-Controller U7 auf die Batterieversorgung um und sichert somit den Datenerhalt. Um diese Funktion zu aktivieren, kann mit Jumper J15 die Versorgungsspannung fuer U13 von VCC auf VPD geändert werden.

Es ergeben sich folgende Konfigurationen:

| Spannungsversorgung E <sup>2</sup> PROM/FRAM | J15       |

|----------------------------------------------|-----------|

| VCC als Versorgungsspannung des              | $1 + 2^*$ |

| E <sup>2</sup> PROM/FRAM                     |           |

| VPD als Versorgungsspannung des              | 2 + 3     |

| E <sup>2</sup> PROM/FRAM                     |           |

<sup>\* =</sup> Default-Einstellung

Tabelle 14: J15 Konfiguration Spannungsversorgung des E<sup>2</sup>PROM/FRAM

## 3.12 J16, J17 Adresse des Seriellen E<sup>2</sup>PROM/FRAM

Mit den Jumpern J16 und J17 wird die Adresse des seriellen E<sup>2</sup>PROM/FRAM konfiguriert. Standardmäßig ist die Adresse des E<sup>2</sup>PROM/FRAM auf 0xA8 eingestellt.

| Adresse des E <sup>2</sup> PROM/FRAM | J16    | J17       |

|--------------------------------------|--------|-----------|

| 0xA8                                 | 2 + 3* | $1 + 2^*$ |

| 0xAA                                 | 1 + 2  | 1 + 2     |

| 0xAC                                 | 2 + 3  | 2 + 3     |

| 0xAE                                 | 1 + 2  | 2 + 3     |

<sup>\* =</sup> Default-Einstellung

Tabelle 15: J16, J17 Konfiguration Adresse Serielles E<sup>2</sup>PROM/FRAM

3.13 J18 Schreibschutz des E<sup>2</sup>PROM/FRAM

Verschiedene auf U13 bestückbare E<sup>2</sup>PROM/FRAM Bausteine verfügen über eine Schreibschutzfunktion<sup>1</sup>. Diese kann über Jumper J18 aktiviert werden. Dazu wird durch Schließen des Jumpers

Pin 7 des seriellen E<sup>2</sup>PROM/FRAM mit VCC verbunden.

| E <sup>2</sup> PROM/FRAM Schreibschutzfunktion         | J18         |  |

|--------------------------------------------------------|-------------|--|

| Schreibschutz des E <sup>2</sup> PROM/FRAM deaktiviert | offen*      |  |

| Schreibschutz des E <sup>2</sup> PROM/FRAM aktiviert   | geschlossen |  |

<sup>\* =</sup> Default-Einstellung

Tabelle 16: J18 Konfiguration E<sup>2</sup>PROM/FRAM Schreibschutz

## 3.14 J19 – J22 Verwendung ICE/Connect

Für die Verwendung von Emulatoren können die Controllersignale /XXP von den im restlichen Modul verwendeten Signalen /XX getrennt und demzufolge von außen eingespeist werden. Hiervon betroffen sind die Signale /PSEN (J19), /RD (J20), /WR (J21) und /RES (J22). Im Auslieferungszustand sind die Jumper J19-J22 geschlossen und somit die Controllersignale mit den Signalen des Modules verbunden.

Bitte informieren Sie sich über das Vorhandensein der Schreibschutzfunktion im Datenblatt des installierten E<sup>2</sup>PROM/FRAM.

## 4 Speichermodelle

Das miniMODUL-537/509 verfügt über einen konfigurierbaren Adreßdekoder, der Anpassungen des Speichermodells per Software zuläßt. Nach einem Hardware-Reset ist ein Default-Speichermodell vorgegeben, welches bereits für eine Vielzahl von Applikationen geeignet ist, jedoch bei Bedarf zu Beginn der jeweiligen Applikation verändert bzw. angepaßt werden kann.

Die Einstellung bzw. Konfiguration des Speichermodells vollzieht sich anhand von zwei Control-, einem Adreß- sowie einem Maskenregister innerhalb des Dekoders. Alle genannten Register sind als Write-Only-Register mit Zugriff im XDATA-Bereich des Controllers ausgeführt. Es existieren zwei verschiedene Adreßbereiche für den Zugriff auf die Register, die durch das Bit IO-SW im Controlregister 1 ausgewählt werden können (*siehe Beschreibung des Bits IO-SW*). Da die Registerinhalte nur geschrieben, nicht aber zurückgelesen werden können, sollte unbedingt eine Kopie aller Registerinhalte in der Applikation gehalten werden. Reservierte Bits dürfen durch das Schreiben der Register nicht verändert werden, der Inhalt sollte unbedingt auf 0 verbleiben. Alle Register werden durch einen Hardware-Reset gelöscht, wodurch die Einstellung des bereits erwähnten Default-Speichermodells gewährleistet wird.

Falls Sie die FlashTools - eine Firmware zur komfortablen on-board Flash-Programmierung - verwenden, so ist zu beachten, daß beim Start Ihrer Anwendersoftware bereits die Adresse FA16 (siehe Controlregister 1) gesetzt wurde. Dieser Sachverhalt ist bei der Anlage der Softwarekopie der Registerinhalte unbedingt zu berücksichtigen. Beachten Sie die Beschreibung der FlashTools in den QuickStart-Instructions.

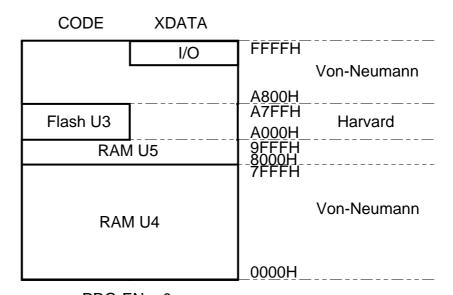

CODE XDATA

I/O

RAM oder EEPROM U5

Flash U3

Flash U4

PRG-EN = 0 VN-EN = 0

Folgendes Bild zeigt das Default-Speichermodell:

Bild 8: Default-Speichermodell nach Hardware-Reset

IO-SW = 0RAM-SW = 0

Hierbei gilt zu beachten, daß jedem der beiden Speicherbausteine U4 und U5 jeweils ein getrennter, 32 kByte großer Speicherbereich im XDATA-Adreßraum des Controllers zukommt. Im Falle einer Bestückung von U4 mit einem 128 kByte RAM-Baustein kann dieser mittels Bank-Latching in Blöcken à 32 kByte angesprochen bzw. umgeschaltet werden. Falls einer der Bausteine U4 und U5 nicht bestückt ist, besteht im entsprechenden Speicherbereich kein Zugriff auf Speicher. Der jeweils aktuelle I/O-Bereich wird im XDATA-Adreßbereich eingeblendet, in ihm besteht kein Zugriff auf einen eventuell vorhandenen Speicherbaustein.

In den folgenden Abschnitten sind die Register des Adreßdekoders zur Anpassung des Speichermodells erläutert .

#### 4.1 Controlregister 1

| Controlregister 1 (Adresse 7C00H / FC00H) |       |      |       |      |      |       |       |

|-------------------------------------------|-------|------|-------|------|------|-------|-------|

| Bit 7                                     |       |      |       |      |      |       | Bit 0 |

| PRG-                                      | IO-SW | RAM- | VN-EN | FA18 | FA17 | FA161 | FA15  |

| EN                                        |       | SW   |       |      |      |       |       |

Tabelle 17: Controlregister 1

Bit im Programmiermodell nicht relevant (s. PRG-EN) Bit nur im Programmiermodell relevant (s. PRG-EN)

PRG-EN:

Dient dem Aktivieren des gesonderten Flash-Programmiermodells (PRG-EN = 1). Dieses Modell wird innerhalb der FlashTools<sup>2</sup> zur Flash-Programmierung verwendet und ist aufgrund der vorhandenen Restriktionen nicht bzw. nur bedingt innerhalb Ihrer Applikation zu verwenden.

In diesem Modell besteht Zugriff auf 32 kByte Flash im Adreßbereich von 0000H-7FFFH sowie auf 32 kByte RAM im Bereich von 8000H-FFFFH. Das Flash ist im XDATA-Bereich lediglich zu schreiben, es kann ausschließlich im CODE-Bereich gelesen werden. Das RAM kann im XDATA-Bereich sowohl gelesen als auch geschrieben werden, das Lesen im CODE-Bereich ist ebenfalls möglich. Nur im Programmiermodell wird die Adreßleitung A15 des Flash ebenfalls dem Controlregister 1 (Bit 0, FA15) entnommen, im Runtime-Modell (PRG-EN = 0) wird die Adreßleitung A15 des Controllers unmittelbar an das Flash durchgeschleift. Die Bits IO-SW und RAM-SW bleiben auch im Programmiermodell relevant, das Bit VN-EN hingegen nicht.

Bei Einsatz der FlashTools - einer Firmware zur komfortablen on-board Flash-Programmierung - ist dieses Bit beim Start Ihrer Anwendung bereits gesetzt. Dies muß bei der Anlage der Softwarekopie Berücksichtigung finden.

Eine Firmware zur komfortablen on-board Flash-Programmierung; beim Erwerb des Moduls incl. Flash-Memory ist diese Software bereits in das Flash einprogrammiert.

*Bild 9* verdeutlicht das Programmiermodell des miniMODUL-537/509 (I/O-Bereich nicht dargestellt):

Bild 9: Flash-Programmiermodell des miniMODUL-537/509

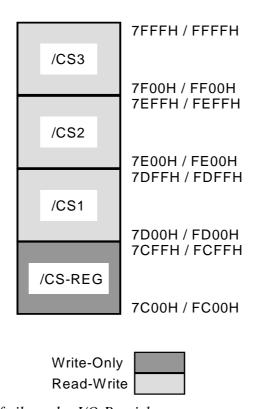

IO-SW:

Mittels dieses Bits kann der I/O-Bereich des Moduls wahlweise in die oberen oder die unteren 32 kByte des Adreßraums gelegt werden. Nach einem Hardware-Reset (IO-SW = 0) liegt der I/O-Bereich von FC00H bis FFFFH, nach Setzen des IO-SW-Bits liegt er im Bereich von 7C00H-7FFFH.

Dieser I/O-Bereich besteht generell aus 4 Blöcken à 256 Bytes. In drei dieser Blöcke stellt der Adreßdekoder jeweils ein vordekodiertes Chip-Select Signal zur Verfügung, das den Hardware-Aufwand zum Anschluß eigener Peripherie an das Modul reduziert. Diese Chip-Select Signale werden (Read-Write XDATA-Zugriffen Zugriffe) im entsprechenden Adreßbereich aktiviert.

Der vierte Block ist reserviert für Zugriffe auf die dekoderinternen Register (Write-Only Zugriffe). Dieser Block steht Ihnen als Anwender daher für den Anschluß externer Perpherie nicht zur Verfügung.

Die Aufteilung des I/O-Bereichs ist folgendem Bild zu entnehmen:

Bild 10: Aufteilung des I/O-Bereichs

Hierbei sind /CS1 bis /CS3 die frei verfügbaren Chip-Select Signale, das Signal /CS-REG ist lediglich ein dekoderinternes Signal, welches für den Zugriff auf die internen Register benötigt wird. Dieses Signal steht Ihnen als Kunde nicht zur Verfügung, der Anschluß jeglicher Peripherie im Gültigkeitsbereich /CS-REG sollte unter allen Umständen unterbleiben, eine korrekte **Funktion** um der FlashTools<sup>1</sup> zur **on-board**-Programmierung des Flash zu gewährleisten.

Die internen Register belegen momentan lediglich die Adressen 7C00H-7C03H bzw. FC00H-FC03H, der Rest des /CS-REG-Blockes bleibt ungenutzt und ist für künftige Erweiterungen reserviert.

#### RAM-SW:

Mittels dieses Bits können die 32 kByte Speicherbereiche der Speicherbausteine U4 und U5 ausgetauscht werden. Nach einem Hardware-Reset (RAM-SW = 0) ist das RAM U4 im Bereich von 0000H bis 7FFFH und das RAM / EEPROM U5 im Bereich von 8000H bis FFFFH adressierbar, nach Setzen des Bits RAM-SW belegt das RAM U4 den Bereich von 8000H-FFFFH und das RAM / EEPROM U5 den Bereich von 0000H-7FFFH. Im jeweils eingestellten I/O-Bereich existiert kein Zugriff auf die Speicherbausteine.

Software-Werkzeug zur on-board Flash-Programmierung, ist bereits bei Auslieferung in das Flash vorprogrammiert.

VN-EN:

Mit diesem Bit werden im Adreßraum des Controllers optionale von Neumann¹-Speicherbereiche freigeschaltet. Nach einem Reset ist per Default eine Harvard²-Architektur vorhanden. Von Neumann-Speicherbereiche sind insbesondere dann sinnvoll, wenn zur Laufzeit Programmcode nachgeladen und anschließend ausgeführt werden soll (z.B. Monitor-Anwendung). Die Lage dieser optionalen von Neumann-Speicherbereiche wird über das Adreßsowie das Maskenregister definiert (siehe unten).

Nach einem Hardware-Reset (VN-EN = 0) sind die Einstellungen im Adreß- und Maskenregister nicht freigeschaltet, d.h., es werden keine von Neumann-Bereiche zur Verfügung gestellt. Nach dem Setzen des Bits (VN-EN = 1) werden die Einstellungen im Adreßsowie im Maskenregister freigeschaltet und in die Zugriffssteuerung einbezogen. Dieses Bit ist nur im Runtime-Modell (PRG-EN 0) = relevant. Programmier-Modell (PRG-EN=1)ist es ohne Bedeutung und wird ignoriert.

Speicherbereich, in dem die Trennung zwischen CODE- und XDATA-Zugriffen aufgehoben ist; beide Zugriffsarten zielen auf den physikalisch gleichen Speicherbaustein, in der Regel ein RAM.

Speicherbereich, in dem CODE- und XDATA-Zugriffe auf physikalisch verschiedene Speicherbausteine abzielen; in der Regel wird für CODE-Zugriffe ein ROM oder Flash, für XDATA-Zugriffe ein RAM eingesetzt.

FA[18..15]: Das Modul verfügt über die Option, einen 512 kByte großen Flash-Baustein aufzunehmen. Da der Adreßraum des Controllers auf 64 kByte beschränkt ist, kann der Rest des Flashs lediglich per Bankumschaltung erreicht werden.

Im Runtime-Modell (PRG-EN = 0) kann das Flash in Bänken à 64 kByte umgeschaltet werden, indem die hohen Adreßleitungen A[18..16] für das Flash per Software vorgegeben werden. Zu diesem Zwecke stellt der Adreßdekoder mit den Registerbits FA[18..16] bereits Latches zur Verfügung, in welche die gewünschten hohen Adressen eingeschrieben werden müssen.

Besondere Beachtung gilt dem Bit FA15, welches lediglich im Programmier-Modell (PRG-EN = 1) relevant wird. Da in diesem Modell auf lediglich 32 kByte Flash zugegriffen werden kann, dient es als Adreßleitung A15 am Flash-Baustein. Im Runtime-Modell (PRG-EN = 0) mit 64 kByte Flash-Bereich wird hingegen die Adreßleitung A15 des Controllers direkt an das Flash durchgeschleift.

Die Funktion der Bits FA[18..16] ist bestückungsabhängig und wirkt sich in der geschilderten Art und Weise nur bei Flash-Bausteinen mit einer Größe von 512 kByte aus.

#### 4.2 Controlregister 2

| Controlregister 2 (Adresse 7C01H / FC01H) |     |     |     |     |     |      |       |  |  |  |

|-------------------------------------------|-----|-----|-----|-----|-----|------|-------|--|--|--|

| Bit 7                                     |     |     |     |     |     |      | Bit 0 |  |  |  |

| <i>N/A</i> <sup>1</sup>                   | N/A | N/A | N/A | N/A | N/A | RA16 | RA15  |  |  |  |

Tabelle 18: Controlregister 2

RA[16..15]: Das Modul verfügt über die Option, einen 128 kByte großen RAM-Baustein auf Position U4 aufzunehmen. Da der Adreßraum des Bausteins U4 im XDATA-Adreßbereich des Controllers auf 32 kByte beschränkt ist, kann der Rest des RAMs lediglich per Bankumschaltung erreicht werden.

Es können 4 Bänke à 32 kByte umgeschaltet werden, indem die hohen Adreßleitungen A[16..15] für das RAM per Software vorgegeben wird. Zu diesem Zweck stellt der Adreßdekoder mit den Registerbits RA[16..15] bereits Latches zur Verfügung, in welche die gewünschte hohen Adressen eingeschrieben werden müssen.

Die Funktion dieser Bits ist bestückungsabhängig und wirkt sich in der geschilderten Art und Weise nur bei RAM-Bausteinen auf U4 mit einer Größe von 128 kByte aus.

\_

<sup>1</sup> N/A: Not Accessible, nicht verfügbar

#### 4.3 Adreßregister

Das Adreßregister (Adresse 7C02H / FC02H) dient zusammen mit dem Maskenregister (*siehe unten*) der Definition von Von Neumann¹-und Harvard²-Speicherbereichen im Adreßraum des Controllers. Durch Setzen des Bits VN-EN im Controlregister 1 werden die Einstellungen freigeschaltet und in die Adreßdekodierung einbezogen (*siehe Controlregister 1*).

Mit beiden Registern wird die Lage von einem bzw. mehreren Harvard-Bereichen konfiguriert, die verbleibenden Bereiche des Adreßraums werden zu von Neumann-Bereichen, in denen die RAMs sowohl bei XDATA- als auch bei CODE-Zugriffen angesprochen wird.

Die Unterscheidung der Bereiche beruht auf einem Vergleich der aktuellen Adressen mit einem vordefinierten Adreßmuster in bestimmten, maskierbaren Bitstellen. Wird eine Übereinstimmung in den relevanten Bitstellen der Adresse erkannt, erfolgen die Zugriffe gemäß einer Harvard-Architektur, andernfalls gemäß einer von Neumann-Architektur.

| Adreßregister (Adresse 7C02H / FC02H) |      |      |      |      |      |       |       |  |  |  |

|---------------------------------------|------|------|------|------|------|-------|-------|--|--|--|

| Bit 7                                 |      |      |      |      |      |       | Bit 0 |  |  |  |

| HA15                                  | HA14 | HA13 | HA12 | HA11 | HA10 | Res.3 | Res.  |  |  |  |

Tabelle 19: Adreßregister

Das Adreßregister dient der Aufnahme des geschilderten Adreßmusters. Jedes Bit des Musters wird mit der entsprechenden Adreßleitung des Controllers verglichen (HA15 mit A15, ..., HA10 mit A10). Dies bedingt durch die zur Verfügung stehenden Adressen A15..A10 eine Granularität bei der Konfiguration von Harvard-Bereichen von min. 1 kByte bewirkt. Blöcke kleiner 1 kByte lassen sich demzufolge nicht einstellen.

\_

Speicherbereich, in dem die Trennung zwischen CODE- und XDATA-Zugriffen aufgehoben ist; beide Zugriffsarten zielen auf den physikalisch gleichen Speicherbaustein, in der Regel ein RAM.

Speicherbereich, in dem CODE- und XDATA-Zugriffe auf physikalisch verschiedene Speicherbausteine abzielen; in der Regel wird für CODE-Zugriffe ein ROM oder Flash, für XDATA-Zugriffe ein RAM eingesetzt.

Reservierte Bits dürfen nicht verändert werden, der Reset-Inhalt 0 muß erhalten bleiben

### 4.4 Maskenregister

Das Maskenregister (Adresse 7C03H / FC03H) dient der Maskierung einzelner Bitstellen des Adreßregisters (siehe oben) für den geschilderten Adreßvergleich. Nach einem Hardware-Reset sind alle Bits des Adreßregisters relevant, durch Setzen einzelner Bits im Maskenregister werden die entsprechenden Bitstellen des Adreßregisters nicht mehr in einen Adreßvergleich einbezogen.

| Maskenregister (Adresse 7C03H / FC03H) |      |      |      |      |      |       |      |

|----------------------------------------|------|------|------|------|------|-------|------|

| Bit 7   Bit 0                          |      |      |      |      |      | Bit 0 |      |

| MA15                                   | MA14 | MA13 | MA12 | MA11 | MA10 | Res.1 | Res. |

Tabelle 20: Maskenregister

0 = relevante Bitstelle im Adreßvergleich

1 = nicht relevante Bitstelle im Adreßvergleich

\_

Reservierte Bits dürfen nicht verändert werden, der Reset-Inhalt 0 muß erhalten bleiben

Folgende Beispiele für die Werte des Adreß- sowie des Maskenregisters verdeutlichen die Funktionsweise:

| AdrR   | AdrReg. |   | MaskReg. |    | eg. | Bemerkung (nur für VN-EN = 1)   |  |

|--------|---------|---|----------|----|-----|---------------------------------|--|

| 1XXXXX | 00      | b | 011111   | 00 | b   | Harvard von 8000H-FFFFH,        |  |

|        |         |   |          |    |     | von Neumann von 0000H-7FFFH     |  |

| 0XXXXX | 00      | b | 011111   | 00 | b   | Harvard von 0000H-7FFFH,        |  |

|        |         |   |          |    |     | von Neumann von 8000H-FFFFH     |  |

| 111111 | 00      | b | 000000   | 00 | b   | Harvard von FC00H-FFFFH,        |  |

|        |         |   |          |    |     | von Neumann von 0000H-FBFFH     |  |

| 010X00 | 00      | b | 000100   | 00 | b   | Harvard von 4000H-43FFH und von |  |

|        |         |   |          |    |     | 5000H-53FFH,                    |  |

|        |         |   |          |    |     | von Neumann von 0000H-3FFFH,    |  |

|        |         |   |          |    |     | von 4400H-4FFFH und von         |  |

|        |         |   |          |    |     | 5400H-FFFFH                     |  |

| 100000 | 00      | b | 000000   | 00 | b   | Harvard von 8000H-83FFH,        |  |

|        |         |   |          |    |     | von Neumann von 0000H-7FFFH     |  |

|        |         |   |          |    |     | und von 8400H-FFFFH             |  |

| 10100X | 00      | b | 000001   | 00 | b   | Harvard von A000H-A7FFH,        |  |

|        |         |   |          |    |     | von Neumann von 0000H-9FFFH     |  |

|        |         |   |          |    |     | und von A800H-FFFFH             |  |

Tabelle 21: Beispiel zur Verwendung von Adreß- und Maskenregister

Grau hinterlegt: Reservierte Bits ohne Funktion für die Adreßdekodierung, (siehe Registerbeschreibungen)

X = don't care aufgrund gesetzter Bits im Maskenregister

Das letzte Beispiel der Tabelle soll anhand des folgenden Bildes nochmals verdeutlicht werden:

PRG-EN = 0 VN-EN = 1 IO-SW = 0 RAM-SW = 0 Adr.-Reg. = 10100X00b Mask.-Reg. = 00000100b

Bild 11: Beispiel-Speichermodell

### 5 Flash Speicher

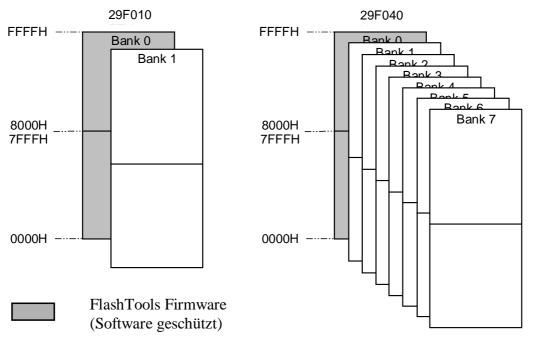

Durch den Einsatz von Flash Speichern als nichtflüchtiger Codespeicher können Sie die Vorteile der modernen Flash-Technik nutzen. Als Flash-Baustein für das miniMODUL-537 steht entweder ein 29F010 mit zwei Bänken à 64 kByte oder ein 29F040 mit acht Bänken à 64 kByte zur Verfügung.

Die Verwendung von Flash Speicher erlaubt die Realisierung einer on-board Programmierung des Moduls. Die Flash Speicher sind mit 5 VDC programmierbar, wodurch keine besondere Programmierspannung benötigt wird. In Bank 0 des Flash ist bereits ein Software-Werkzeug (PHYTEC FlashTools) integriert, welches diese on-board Reprogrammierung des Flashs ermöglicht. Dadurch ist die maximale Göße des nutzbaren Speichers 64 kByte (29F010) bzw. 448 kByte (29F040) (siehe Bild 12).

Sollte die FlashTools Firmware ohne gleichwertigen Ersatz aus dem Flash gelöscht werden, so ist eine Reprogrammierung nicht mehr möglich!

Bild 12: Speicherbereiche des Flash

Beachten Sie bitte, daß sich die Software selbst gegen ein absichtliches oder versehentliches Löschen bzw. Überprogrammieren schützt. Da der bei den verwendeten Flashtypen gebotene Hardware-Schutzmechanismus allerdings nicht verwendet wird, beschränkt sich der Schutz auf Software-Maßnahmen. Sie sollten beim eventuellen Einsatz eigener Programmieralgorithmen oder Werkzeuge unbedingt dafür Sorge tragen, daß ein Programmierwerkzeug im Flash verbleibt.

Der Einsatz des Flash-Bausteins als einziger Code-Speicher des Moduls bewirkt, daß das Flash nicht oder nur sehr bedingt zur nichtflüchtigen Ablage von Daten geeignet ist. Dies ist durch die interne Architektur der Flash-Bausteine verursacht, da während des Flash-internen Programmierprozesses ein Lesen von Daten aus dem Baustein unmöglich ist. Demzufolge muß für eine Flashprogrammierung die Programmausführung aus dem Flash heraus verlagert werden Neumann-RAM), was Regel (z.B. in von in der einschneidenden Eingriff in den "normalen" Programmablauf gleichkommt.

Nach Stand der Technik zur Drucklegung dieses Manuals weisen die Flash-Bausteine eine Lebenserwartung von min. 100000 Lösch-/Programmierzyklen auf.

## 6 Batteriepufferung

Die zur Batteriepufferung nötige Batterie ist für die Grundfunktion des miniMODUL-537/509 nicht zwingend erforderlich. Allerdings bietet sich die Batteriepufferung als eine günstige und einfache Möglichkeit des nichtflüchtigen Abspeicherns von Daten an.

Der VBAT-Eingang am Modulpin 42 ist für den Anschluß einer externen Batterie vorgesehen. Wir empfehlen nach dem Stand der Technik zur Drucklegung dieses Manuals Lithium-Batterien, da diese hohe Kapazitäten bei sehr geringer Selbstentladung aufweisen. Die bestückten RAM-Bausteine werden bei fehlender Versorgungsspannung VCC von einer eventuell vorhandenen Batterie über VBAT gespeist.

Besondere Beachtung sollte hierbei die Bestückung eines EEPROMs an Position U5 des Moduls finden. Dieser Baustein ist aufgrund seiner Stromaufnahme sowie dem mit der EEPROM-Technologie verbundenen Datenerhalt nicht für eine Versorgung durch eine Batterie geeignet. In diesem Fall muß daher der Jumper J2 (siehe Kapitel 3.2) entsprechend konfiguriert werden, da andernfalls eine vorzeitige Entladung einer angeschlossenen Batterie erfolgt.

Die Stromaufnahme hängt von den verwendeten Bausteinen bzw. dem Speicherausbau ab. Sie beträgt bei den verwendeten Bausteinen pro RAM-Baustein typisch 1 µA.

Aus Gründen der Betriebssicherheit möchten wir jedoch darauf hinweisen, daß trotz Batteriepufferung eine Veränderung der Dateninhalte im RAM infolge äußerer Störeinflüsse nicht absolut ausgeschlossen werden kann.

### 7 Echtzeituhr RTC-8564 (U12)

Für Echtzeitanwendungen ist das miniMODUL-537/509 mit einer Echtzeituhr des Typs RTC-8564 ausgestattet. Diese Echtzeituhr bietet die folgenden Funktionen:

- Serielle Kommunikation über I<sup>2</sup>C Bus

- Stromaufnahme

Bus aktiv: max. 50 mA

Bus inaktiv, CLKOUT = 32 kHz: max. 1,7 A

Bus inaktiv, CLKOUT = 0 kHz: max.  $0.75 \mu A$

- Uhrfunktion mit 4-Jahres Kalender

- Jahrhundertbit

- Universeller Timer mit Alarm- und Überlaufanzeige

- 24-Stunden Format

- Automatische Word-Adressen Inkrementierung

- Programmierbare Alarm-, Timer- und Interruptfunktion

Wird das miniMODUL-537/509 über eine Batterie gepuffert, läuft die Echtzeituhr auch nach Ausfall der Spannungsversorgung des Boards weiter.

Die Programmierung der Echtzeituhr erfolgt über I<sup>2</sup>C-Bus (Adresse 0xA2 = 10100010), der mit Hilfe der Ports P6.4 (SCL) und P6.5 (SDA) realisiert ist. Zusätzlich verfügt die Echtzeituhr über einen Interruptausgang, der mit der Stiftleiste X1A30B (60) verbunden ist. Ereignisse für einen Interrupt können ein Uhrenalarm, Timerüberlauf bzw. ein ein Timeralarm, ein Alarm Ereigniszählers sein. Alle Interrupts müssen durch Software gelöscht werden. Durch die Interruptfunktion ist die Echtzeituhr für die unterschiedlichsten Applikationen verwendbar. (Weitere Informationen über die Register der Echtzeituhr finden Sie im beigelegten Datenblatt.)

#### **Achtung!**

Nach Anlegen der Versorgungsspannung bzw. nach einem Reset generiert die Echtzeituhr **keinen** Interrupt, da sie hierfür erst initialisiert werden muß.

### 8 Serielles EEPROM/FRAM (U13)

Das miniMODUL-537/509 verfügt über einen nichtflüchtigen Speicher mit einem seriellen Interface (I<sup>2</sup>C-Interface) zur Ablage von Konfigurationsdaten. Je nach Bestückungsvariante kann dieser Speicher mit einem EEPROM in der Größe von 4 - 32 kByte oder mit einem FRAM bestückt werden.

Eine Beschreibung des I<sup>2</sup>C-Protokolls ist dem Datenblatt des Bauteins zu entnehmen.

*Tabelle* 22 gibt einen Überblick zu bestückbaren Bausteinen zum Zeitunkt der Drucklegung des Handbuchs.

| Speichertyp | Größe    | Baustein | Hersteller |

|-------------|----------|----------|------------|

| EEPROM      | 4 kByte  | AT25320  | ATMEL      |

|             | 8 kByte  | AT25640  | ATMEL      |

|             | 32 kByte | 24WC256  | CATALYST   |

| FRAM        | 512 Byte | FM25040  | RAMTRON    |

|             | 8 kByte  | FM25160  | RAMTRON    |

Tabelle 22: Bestückungsoptionen für U13

Verschiedene E<sup>2</sup>PROM/FRAM verfügen über eine Schreibschutzfunktion<sup>1</sup>. Diese kann über Jumper J18 aktiviert werden. Dazu wird durch Schließen des Jumpers Pin 7 des seriellen E<sup>2</sup>PROM/FRAM mit VCC verbunden.

| Schreibschutz des E <sup>2</sup> PROM/FRAM | J18         |

|--------------------------------------------|-------------|

| Schreibschutz ist deaktiviert              | offen*      |

| Schreibschutz ist aktiviert                | geschlossen |

<sup>\* =</sup> Default-Einstellung

Tabelle 23: E<sup>2</sup>PROM/FRAM Schreibschutz.

© PHYTEC Meßtechnik GmbH 2002 L-627d\_1 39

<sup>1:</sup> Bitte informieren Sie sich über das Vorhandensein der Schreibschutzfunktion im Datenblatt des installierten E<sup>2</sup>PROM/FRAM.

Mit Jumper J16 und J17 wird die Adresse des seriellen  $E^2PROM/FRAM$  konfiguriert. Standardmäßig ist die Adresse des  $E^2PROM/FRAM$  auf 0xA8 eingestellt.

Folgende Alternativen sind möglich:

| Adresse des E <sup>2</sup> PROM/FRAM | J16    | J17       |

|--------------------------------------|--------|-----------|

| 0xA8                                 | 2 + 3* | $1 + 2^*$ |

| 0xAA                                 | 1 + 2  | 1 + 2     |

| 0xAC                                 | 2 + 3  | 2 + 3     |

| 0xAE                                 | 1 + 2  | 2 + 3     |

<sup>\* =</sup> Default-Einstellung

Tabelle 24: E<sup>2</sup>PROM/FRAM Adresse

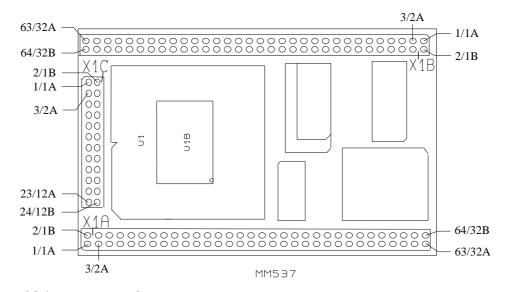

#### 9 Technische Daten

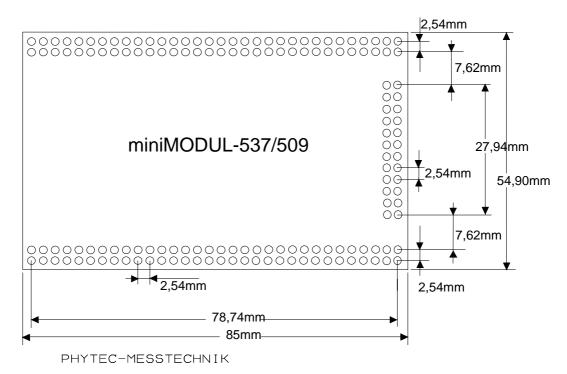

Das miniMODUL-537/509 ist in seinen mechanischen Abmessungen in *Bild 13* dargestellt. Die Höhe des Moduls beträgt ohne Stiftleisten ca. 10 mm. Hierbei tragen die Bauteile jeweils ca. 3 mm auf der Platinenunterseite sowie ca. 5,5 mm auf der Oberseite auf. Die Platine selbst ist ca. 1,5 mm stark und besteht aus sechs Lagen.

Bild 13: Mechanische Abmaße

#### Weitere Daten:

- Modulgröße 54,90 mm x 85 mm ±0,01 mm

- Gewicht ca. 44 g bei Maximalausbau mit 160 kByte RAM, gesockeltem Flash und gesockeltem Controller; Gewicht ca. 32 g bei Standardausbau mit 32 kByte RAM, ohne Sockel

- Lagertemperaturbereich -40°C bis +90°C

- Betriebstemperaturbereich Standard 0°C bis +70°C, erweitert -40° bis +85°C

- Luftfeuchtebereich max. 95 % r.F. nicht kondensierend

- Betriebsspannungen 5 V ±5 %, VBAT 3 V ±20 %

- Stromaufnahme max. 140 mA, typ. 100 mA bei miniMODUL-537 mit 12 MHz Oszillatorfrequenz und 128 kByte RAM bei 20°C

- Stromaufnahme bei Batteriepufferung max. 10 μA pro RAM-Baustein, typisch 1 μA pro RAM-Baustein bei 20°C

# 10 Hinweise zum Umgang mit dem Modul

Beim Wechsel eines gesockelten Controllers ist zu beachten, daß der Sockel nicht durch unsachgemäße Werkzeuge beschädigt wird. Bitte verwenden Sie unbedingt ein passendes PLCC-Aushebelwerkzeug.

Von einem Wechsel des Quarzes oder Oszillators ist aufgrund der hohen Packungsdichte des Moduls generell abzuraten. Sollte dies wider Erwarten vonnöten sein, so ist zu beachten, daß beim Auslöten die Leiterplatte sowie umliegende Bauteile oder Sockel nicht beschädigt werden. Die Lötpads können sich bei Überhitzung von der Platine ablösen, wodurch das Modul unbrauchbar wird. Erhitzen Sie vorsichtig paarweise die benachtbarten Anschlüsse, nach einigen Wechseln können Sie das Bauteil mit der Lötspitze abheben. Alternativ kann ein entsprechendes Heißluft-Werkzeug zur Erhitzung der Lötstellen verwendet werden.

# Index

| /                        | Flash-Programmiermodell28  |

|--------------------------|----------------------------|

| /PSEN24                  | H                          |

| /RD24                    | Hinweise zum Umgang mit    |

| /RES24                   | dem Modul50                |

| /WR24                    | I                          |

| $oldsymbol{A}$           | I/O-Bereich29              |

| Abmessungen48            | I <sup>2</sup> C-Bus44     |

| Adreßdekoder26           | Internes Programmiermodell |

| Adreßregister36          | beim C50922                |

| Anschlußbelegung8        | IO-SW29                    |

| Anschlüsse8              | J                          |

| В                        | J113                       |

| Bank-Latching27, 35      | J1019                      |

| Batteriepufferung43      | J1119                      |

| <i>C</i>                 | J1220                      |

|                          | J1320                      |

| Chip-Enable RTC7242320   | J1422                      |

| Controlregister 128      | J1522                      |

| Controlregister 235      | J1623                      |

| D                        | J1723                      |

| Default-Speichermodell26 | J1824<br>J1924             |

| $oldsymbol{E}$           | J214                       |

| _                        | J2024                      |

| E²PROM/FRAM Adresse23    | J2124                      |

| Schreibschutz24          | J2224                      |

| Versorgung22             | J314                       |

| Echtzeituhr              | J416                       |

| EMV1                     | J516                       |

| ESD1                     | J616                       |

| $oldsymbol{F}$           | J717                       |

|                          | J817<br>J917               |

| FA[1815]34               | Jumper12                   |

| Features5                | Jumper12                   |

| Flash Speicher41         |                            |

| M                             | RTC-856444                                            |

|-------------------------------|-------------------------------------------------------|

| Maskenregister37              | S                                                     |

| o                             | Schnittstellen16                                      |

| Oszilator-Watchdog16          | Serielle Schnittstelle 0                              |

| P                             | Serielle Schnittstelle 117<br>Serielles EEPROM/FRAM46 |

| Pinout11                      | Speichermodelle26                                     |

| Power-Saving-Modes14          | T                                                     |

| PRG-EN28                      | Technische Daten48                                    |

| Programmspeicher, Auswahl 13  | Technische Daten48                                    |

| R                             | $oldsymbol{U}$                                        |

| RA[1615]35                    | U1244                                                 |

| RAM-SW                        | U1346                                                 |

| Register des Adreßdekoders 27 | $oldsymbol{V}$                                        |

| RS-232-Steuerung20            | VN-EN33                                               |

| RS-232-Transceiver 16         | VIN-EIN53                                             |

| RS-485-Steuerung17            | W                                                     |

| RS-485-Transceiver 17         | Watchdog-Timer14                                      |

| <b>Dokument:</b>                           | miniMODUL-537/509                         |       |  |  |

|--------------------------------------------|-------------------------------------------|-------|--|--|

| Dokumentnu                                 | ımmer: L-627d_1, Juli 2002                |       |  |  |

| Wie würden Sie dieses Handbuch verbessern? |                                           |       |  |  |

|                                            |                                           |       |  |  |

|                                            |                                           |       |  |  |

| Haben Sie in                               | diesem Handbuch Fehler entdeckt?          | Seite |  |  |

|                                            |                                           |       |  |  |

|                                            |                                           |       |  |  |

|                                            |                                           |       |  |  |

| Eingesandt v Kundennumn                    |                                           |       |  |  |

| Name:                                      |                                           |       |  |  |

| Firma:                                     | -                                         |       |  |  |

| Adresse:                                   |                                           |       |  |  |

| Einsenden an                               |                                           |       |  |  |

|                                            | PHYTEC Technologie Holding AG             |       |  |  |

|                                            | Postfach 100403<br>D-55135 Mainz, Germany |       |  |  |

|                                            | Fax: +49 (6131) 9221-33                   |       |  |  |